503.40146X0

•

Applicant(s): AOYAMA, et al Serial No.: Not assigned Filed: May 25, 2001 Title: DISPLAY DEVICE Group: Not assigned

## LETTER CLAIMING RIGHT OF PRIORITY

Honorable Commissioner of Patents and Trademarks Washington, D.C. 20231 May 25, 2001

Sir:

Under the provisions of 35 USC 119 and 37 CFR 1.55, the applicant(s) hereby claim(s) the right of priority based on Japanese Patent Application No.(s) 2000-173567 filed June 9, 2000.

A certified copy of said Japanese Application is attached.

Respectfully submitted,

ANTONELLI, TERRY, STOUT & KRAUS, LLP

Melvin Kraus Registration No. 22,466

MK/amr Attachment (703) 312-6600 別紙添付の書類に記載されている事項は下記の出願書類に記載されている事項と同一であることを証明する。

PATENT OFFICE JAPANESE GOVERNMENT

符

E

許

厅

This is to certify that the annexed is a true copy of the following application as filed with this Office.

出願年月日 Date of Application: 2000年 6月 9日 出願番号 Application Number: 特願2000-173567

B

太

出 願 人 Applicant (s):

Ç

株式会社日立製作所

2000年11月17日

| -           | 【書類名】    | 特許願               |

|-------------|----------|-------------------|

| _           | 【整理番号】   | PE27798           |

|             | 【提出日】    | 平成12年 6月 9日       |

|             | 【あて先】    | 特許庁長官    殿        |

|             | 【国際特許分類】 | G09G 3/18         |

|             | 【発明者】    |                   |

| <b>4</b> 56 | 【住所又は居所】 | 茨城県日立市大みか町七丁目1番1号 |

| *           |          | 株式会社 日立製作所 日立研究所内 |

| · . ₩       | 【氏名】     | 青山 哲也             |

|             | 【発明者】    |                   |

|             | 【住所又は居所】 | 茨城県日立市大みか町七丁目1番1号 |

|             |          | 株式会社 日立製作所 日立研究所内 |

|             | 【氏名】     | 小村 真一             |

|             | 【発明者】    |                   |

|             | 【住所又は居所】 | 茨城県日立市大みか町七丁目1番1号 |

|             |          | 株式会社 日立製作所 日立研究所内 |

|             | 【氏名】     | 檜山 郁夫             |

|             | 【発明者】    |                   |

|             | 【住所又は居所】 | 茨城県日立市大みか町七丁目1番1号 |

| -           |          | 株式会社 日立製作所 日立研究所内 |

| a<br>t      | 【氏名】     | 山本恒典              |

| 34<br>-     | 【発明者】    |                   |

|             | 【住所又は居所】 | 茨城県日立市大みか町七丁目1番1号 |

|             |          | 株式会社 日立製作所 日立研究所内 |

|             | 【氏名】     | 金子 好之             |

|             | 【発明者】    |                   |

|             | 【住所又は居所】 | 茨城県日立市大みか町七丁目1番1号 |

|             |          | 株式会社 日立製作所 日立研究所内 |

|             | 【氏名】     | 池田光二              |

出証特2000-3095497

.

【発明者】

-

|           | •                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 【住所又は居所】  | 茨城県日立市大みか町七丁目1番1号                                                                                                                                                                                                                                                                                                                                                                                       |

|           | 株式会社 日立製作所 日立研究所内                                                                                                                                                                                                                                                                                                                                                                                       |

| 【氏名】      | 伊東理                                                                                                                                                                                                                                                                                                                                                                                                     |

| 【発明者】     |                                                                                                                                                                                                                                                                                                                                                                                                         |

| 【住所又は居所】  | 茨城県日立市大みか町七丁目1番1号                                                                                                                                                                                                                                                                                                                                                                                       |

|           | 株式会社 日立製作所 日立研究所内                                                                                                                                                                                                                                                                                                                                                                                       |

| 【氏名】      | 佐藤 秀夫                                                                                                                                                                                                                                                                                                                                                                                                   |

| 【発明者】     |                                                                                                                                                                                                                                                                                                                                                                                                         |

| 【住所又は居所】  | 茨城県日立市大みか町七丁目1番1号                                                                                                                                                                                                                                                                                                                                                                                       |

|           | 株式会社 日立製作所 日立研究所内                                                                                                                                                                                                                                                                                                                                                                                       |

| 【氏名】      | 廣田 昇一                                                                                                                                                                                                                                                                                                                                                                                                   |

| 【特許出願人】   |                                                                                                                                                                                                                                                                                                                                                                                                         |

| 【識別番号】    | 000005108                                                                                                                                                                                                                                                                                                                                                                                               |

| 【氏名又は名称】  | 株式会社 日立製作所                                                                                                                                                                                                                                                                                                                                                                                              |

| 【代理人】     |                                                                                                                                                                                                                                                                                                                                                                                                         |

| 【識別番号】    | 100098017                                                                                                                                                                                                                                                                                                                                                                                               |

| 【弁理士】     |                                                                                                                                                                                                                                                                                                                                                                                                         |

| 【氏名又は名称】  | 吉岡 宏嗣                                                                                                                                                                                                                                                                                                                                                                                                   |

| 【手数料の表示】  |                                                                                                                                                                                                                                                                                                                                                                                                         |

| 【予納台帳番号】  | 055181                                                                                                                                                                                                                                                                                                                                                                                                  |

| 【納付金額】    | 21,000円                                                                                                                                                                                                                                                                                                                                                                                                 |

| 【提出物件の目録】 |                                                                                                                                                                                                                                                                                                                                                                                                         |

| 【物件名】     | 明細書 1                                                                                                                                                                                                                                                                                                                                                                                                   |

| 【物件名】     | 図面 1                                                                                                                                                                                                                                                                                                                                                                                                    |

|           |                                                                                                                                                                                                                                                                                                                                                                                                         |

| 【物件名】     | 要約書 1                                                                                                                                                                                                                                                                                                                                                                                                   |

|           | 【発明者】<br>【住所又は居所】<br>【氏名】<br>【発明者】<br>【住所又は居所】<br>【住所又は居所】<br>【住所又は居所】<br>【代書出願人】<br>【特許出願人】<br>【総計工願人】<br>【代理人】<br>【代理人】<br>【代理人】<br>【代理人】<br>【代理人】<br>【代理人】<br>【代理人】<br>【代理人】<br>【代理人】<br>【代理人】<br>【代理人】<br>【代理人】<br>【代理人】<br>【代理人】<br>【代理人】<br>【代理人】<br>【代理人】<br>【代理人】<br>【代理人】<br>【代理人】<br>【代理人】<br>【代理人】<br>【代理人】<br>【代理人】<br>【代理人】<br>【代理人】<br>【代理人】<br>【代理人】<br>【代理人】<br>【代理人】<br>【代理人】<br>【代理人】 |

【書類名】 明細書

【発明の名称】 表示装置

【特許請求の範囲】

【請求項1】 n(nは2以上の自然数)個の複数画素を1ブロック単位とし、前記ブロック単位中の前記複数画素を同時に選択し、空間周波数の異なる特定 パターンを1ないし複数個加え合わせて画像を表示する表示モジュールと、前記 表示モジュールを制御する表示制御装置と、前記ブロック毎に画像信号から空間 周波数の異なる前記特定パターンを重み付けして発生させる演算回路と、前記画 像信号を発生する画像発生装置とを備えた表示装置。

【請求項2】 請求項1に記載の表示装置において、

前記演算回路が、前記ブロック毎に画像信号から空間周波数の異なるn個の前 記特定パターンを重み付けして発生させる手段であり、

前記表示モジュールが、前記特定パターンをNp(nより小さい自然数)個加え 合わせて画像を表示する手段である

ことを特徴とする表示装置。

【請求項3】 請求項2に記載の表示装置において、

前記特定パターンを加え合わせる個数Npを変更する手段として圧縮率調整装置を備えた

ことを特徴とする表示装置。

【請求項4】 請求項2または3に記載の表示装置において、

前記ブロックによって加え合わせる前記特定パターンの種類の数を変更する手 段として高圧縮演算回路を備えた

ことを特徴とする表示装置。

【請求項5】 請求項1ないし4のいずれか一項に記載の表示装置において

前記表示モジュールが、前記画素をマトリクス状に配列したパネルと、信号ド ライバと、走査ドライバと、対向信号ドライバとを備え、

前記信号ドライバには信号線を接続し、前記走査ドライバには走査線を接続し、 前記対向信号ドライバには対向信号線を接続し、

前記画素が、信号電極と対向信号電極とスイッチ素子とを備え、

前記信号電極には前記スイッチ素子を介して前記信号線を接続し、

前記対向信号電極には前記対向信号線を接続し、

同一の前記ブロックに含まれて同一の行の前記画素に備えられた前記信号電極 には同一の第1電位を与え、同一の前記ブロックに含まれて同一の列の前記画素 に備えられた前記対向信号電極には同一の第2電位を与え、

前記ブロックが前記第1電位と前記第2電位とにより前記特定パターンを形成し、

同一の行に含まれる前記画素に備えられた前期対向信号電極には共通の前記対 向信号線を接続した

ことを特徴とする表示装置。

【請求項6】 請求項2ないし4のいずれか一項に記載の表示装置において

前記表示モジュールは、前記画素がマトリクス状に配列したパネルと、信号ド ライバと、走査ドライバと、対向信号ドライバとを備え、

前記信号ドライバには信号線を接続し、前記走査ドライバには走査線を接続し、前記対向信号ドライバには対向信号共通線を接続し、前記対向信号共通線には 対向信号線を接続し、

前記画素は信号電極と対向信号電極とスイッチ素子とを備え、

前記信号電極には前記スイッチ素子を介して前記信号線を接続し、前記対向信 号電極には前記対向信号線を接続し、

同一の前記ブロックに含まれて同一の行の前記画素に備えられた前記信号電極 には同一の第1電位を与え、同一の前記ブロックに含まれて同一の列の前記画素 に備えられた前記対向信号電極には同一の第2電位を与え、

前記ブロックが前記第1電位と前記第2電位とにより前記特定パターンを形成 し、

異なる前記ブロックに含まれる前記画素に備えられた前記対向信号電極には異 なる前記対向信号線を接続した

ことを特徴とする表示装置。

【請求項7】 請求項2ないし4のいずれか一項に記載の表示装置において

前記表示モジュールは、前記画素がマトリクス状に配列したパネルと、信号ド ライバと、走査ドライバと、対向信号ドライバとを備え、

前記信号ドライバには信号線を接続し、前記走査ドライバには走査線を接続し、前記対向信号ドライバには対向信号共通線を接続し、前記対向信号共通線には 対向信号線を接続し、

前記画素は信号電極と対向信号電極とスイッチ素子とを備え、

前記信号電極には前記スイッチ素子を介して前記信号線を接続し、前記対向信 号電極には前記対向信号線を接続し、

同一の前記ブロックに含まれて同一の行の前記画素に備えられた前記信号電極 には同一の第1電位を与え、同一の前記ブロックに含まれて同一の列の前記画素 に備えられた前記対向信号電極には同一の第2電位を与え、

前記ブロックが前記第1電位と前記第2電位とにより前記特定パターンを形成 し、

異なる前記ブロックに含まれる前記画素に備えられた前記対向信号電極には異 なる前記対向信号線を接続し、

同一の前記ブロックに含まれて異なる行の前記画素に備えられた前記対向信号 電極にはそれぞれ異なる前記対向信号線を接続した

ことを特徴とする表示装置。

【請求項8】 請求項1ないし7のいずれか一項に記載の表示装置において

前記ブロックの行方向の画素数が前記ブロックの列方向の画素数よりも多い ことを特徴とする表示装置。

【請求項9】 請求項2ないし8のいずれか一項に記載の表示装置において

前記ブロックを形成する前記複数画素の組み合わせが可変である ことを特徴とする表示装置。

【請求項10】 請求項1ないし9のいずれか一項に記載の表示装置におい

て、

前記表示モジュールが、投射型ディスプレイであり、

前記投射型ディスプレイが、前記特定パターンを表示する投射パターン表示源と 、パターン表示素子とを備え、

前記パターン表示素子が、透明電極が形成された一対の基板と前記透明電極上 に形成された光導電層と前記一対の基板に狭持された液晶層とを備えた

ことを特徴とする表示装置。

【請求項11】 請求項2ないし10のいずれか一項に記載の表示装置において、

前記表示モジュールが、前記特定パターンを順次表示し画像を加え合わせて表 示する手段である

ことを特徴とする表示装置。

【請求項12】 請求項2ないし10のいずれか一項に記載の表示装置において、

前記表示モジュールが、前記特定パターンを画素内で演算し加え合わせて画像 を表示する手段である

ことを特徴とする表示装置。

【請求項13】 請求項12に記載の表示装置において、

前記表示モジュールは、前記画素をマトリクス状に配列したパネルと、信号ド ライバと、走査ドライバと、共通電極ドライバとを備え、

前記信号ドライバには信号線を接続し、前記走査ドライバには走査線を接続し

、共通電極ドライバには共通電極線を接続し、

前記各画素には前記特定パターンを加え合わせる加減算器を備え、

前記加減算器には前記特定パターンを加え合わせる個数Npに等しい数の前記 信号線を接続した

ことを特徴とする表示装置。

【請求項14】 請求項13に記載の表示装置において、

前記パネルは前記画素に液晶を備えた液晶パネルであり、

前記各画素には前記信号線を介して送られる信号をホールドする容量素子を、

4

## 出証特2000-3095497

前記特定パターンを加え合わせる個数Np個以上備え、

前記容量素子と前記液晶の容量とを結合する手段を備えた

ことを特徴とする表示装置。

【請求項15】 請求項2ないし12のいずれか一項に記載の表示装置において、

前記画素を構成するそれぞれの回路が、デジタル信号のサンプルホールド手段 と、アナログ信号のサンプルホールド手段とを備えた

ことを特徴とする表示装置。

【請求項16】 請求項15に記載の表示装置において、

前記デジタル信号のサンプルホールド手段にホールドされた信号に応じて、前 記アナログ信号のサンプルホールド手段にホールドされた信号を書き換え、

同一の前記ブロックに含まれる前記画素には、同一の信号を与える

ことを特徴とする表示装置。

【請求項17】 請求項1ないし16のいずれか一項に記載の表示装置において、

前記画像発生装置が、前記演算回路を含む

ことを特徴とする表示装置。

【請求項18】 請求項1ないし16のいずれか一項に記載の表示装置において、

前記表示制御装置が、前記演算回路を含む

ことを特徴とする表示装置。

【請求項19】 請求項1ないし16のいずれか一項に記載の表示装置において、

前記表示モジュールが、前記演算回路を有する ことを特徴とする表示装置。

【請求項20】 請求項1ないし19のいずれか一項に記載の表示装置において、

前記表示モジュールが、液晶モジュールである ことを特徴とする表示装置。

【発明の詳細な説明】

[0001]

【発明の属する技術分野】

本発明は、表示装置に係り、特に、高精細な表示装置および高駆動周波数の表示装置に関する。

[0002]

【従来の技術】

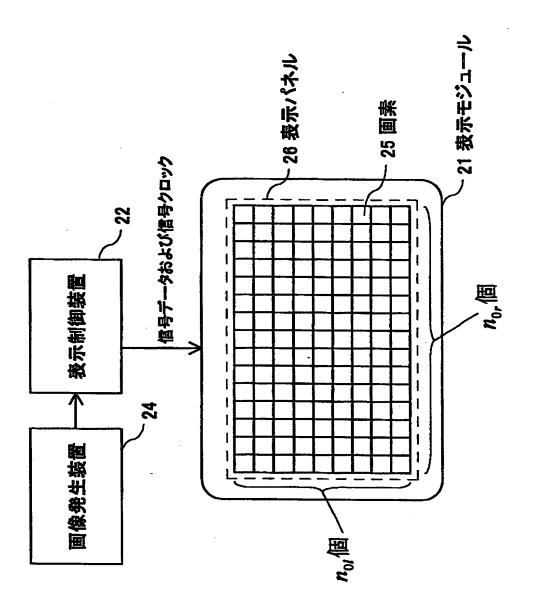

図2は、従来の表示装置の一般的構成を示す図である。液晶表示装置やプラズ マディスプレイパネルなどの従来の表示装置は、図2に示すように、画素25が 行方向にn<sub>01</sub>個、列方向にn<sub>0r</sub>個だけマトリクス状に配列した表示パネル2 6を備えた表示モジュール21と、表示モジュール21を制御する表示制御装置 22と、画像信号を発生する画像発生装置24とを備えている。

[0003]

表示パネル26において、駆動周波数  $f_H$ で画像を表示するとき、表示モジュ ール21に送られる信号は、周期1/ $f_H$ 毎に $n_{01}$ × $n_{0r}$ 個だけ必要になり 、表示制御装置22から表示モジュール21に信号を送るための信号クロック周 波数  $f_s$ は、数式1のようになる。ここでは、帰線期間などは、考慮しないこと にする。

[0004]

【数1】

## $f_s = n_{0l} \times n_{0r} \times f_H$

信号クロック周波数は、画素数および駆動周波数に比例するので、表示装置の 高精細化による画素数の増大や高速駆動に伴い、信号クロック周波数が増大する

[0005]

次に、データ信号の書き込みについて、アクティブマトリクス型液晶表示装置 を例にとって説明する。

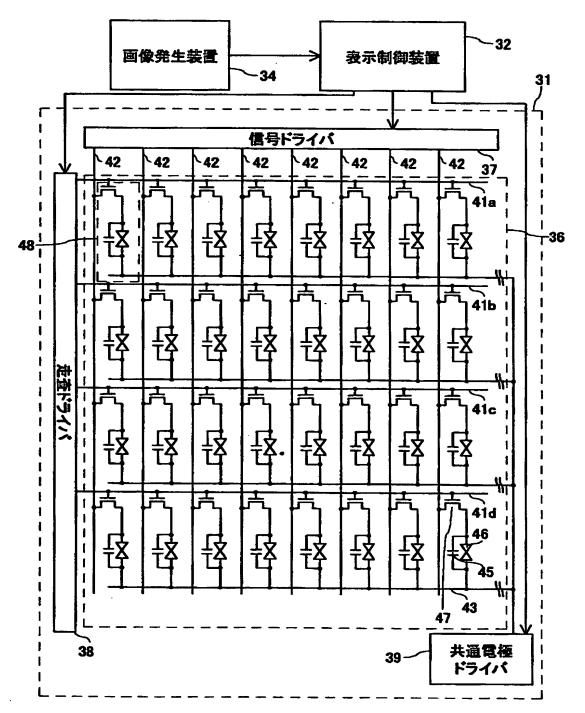

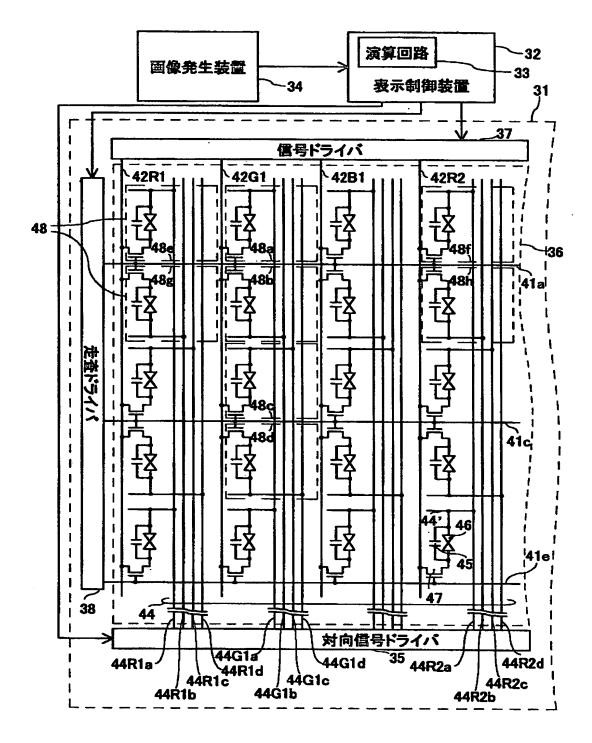

図3は、従来の表示装置の系統構成および表示パネル内の構成を示す図である 。従来のアクティブマトリクス型液晶表示装置は、図3に示すように、画素48 がマトリクス状に配列した表示パネル36と信号ドライバ37と走査ドライバ3 8と共通電極ドライバ39とを備えた表示モジュール31と、表示モジュール3 1を制御する表示制御装置32と、画像信号を発生する画像発生装置34とを備 えている。

[0007]

[0006]

信号ドライバ37には、信号線42が接続され、走査ドライバ38には、走査 線41a,41b,41c,41d,…が接続され、共通電極ドライバ39には 、共通電極線43が接続されている。画素48には、薄膜トランジスタ(TFT) 47と容量素子45と液晶46に電圧を印加するための信号電極(図示せず)およ び対向信号電極(図示せず)とが備えられており、信号電極は、TFT47を介し て信号線42に接続され、対向信号電極は、共通電極線43に接続されている。

[0008]

液晶46に電圧を印加する駆動方法は、以下に説明するように線順次走査であ る。走査ドライバ38によって、走査線41a,41b,41c,41d,…に アドレス信号が順次に印加され、走査される。アドレス信号が印加された走査線 に接続されている1行全てのTFT47は、オンになり、信号ドライバ37によ って信号線42に印加された電位と共通電極ドライバ39によって共通電極線4 3に印加された電位との電位差が液晶46および容量素子45に印加される。

[0009]

行方向にn<sub>01</sub>個の画素48があり、すなわちn<sub>01</sub>本の走査線がある表示パ ネル36を駆動周波数f<sub>H</sub>で線順次走査駆動する場合、周期1/f<sub>H</sub>で全走査線 を走査するため、走査線1本当りにアドレス信号が与えられる時間、すなわちデ ータ信号書き込み時間t<sub>s</sub>は、数式2のようになる。ここでは、帰線期間などは 、考慮しないことにする。

[0010]

【数2】

したがって、データ信号書き込み時間は、走査線数および駆動周波数に反比例 する。すなわち、表示装置の高精細化による走査線数の増大や高速駆動化に伴っ て、データ信号書き込み時間は、減少し、信号データの書き込み不足などの問題 が生じやすくなる。

[0011]

【発明が解決しようとする課題】

以上のように、従来の表示装置では、表示モジュールの画素数の増大や駆動周 波数の増大に伴って信号クロック周波数が増大する。そのため、消費電力が増大 するとともに、高速動作が可能なICが要求される。

[0012]

また、線順次走査駆動を利用した表示装置では、行方向の画素数の増大や駆動 周波数の増大に伴って、1行を選択する時間が減少する。結果として、信号を書 き込む時間が減少する。

[0013]

さらに、精細度の増大に伴って、配線に伴う面積の画素面積に対する比率が増 大し、開口率が低下する。

【0014】

本発明の目的は、信号クロック周波数を低下させ、信号書き込み時間を増大さ せ、開口率を上げ、高精細表示かつ高速動画表示が可能な表示装置を提供するこ とである。

[0015]

【課題を解決するための手段】

本発明は、上記目的を達成するために、n(nは2以上の自然数)個の複数画素 を1ブロック単位とし、ブロック単位中の複数画素を同時に選択し、空間周波数 の異なる特定パターンを1ないし複数個加え合わせて画像を表示する表示モジュ

ールと、表示モジュールを制御する表示制御装置と、ブロック毎に画像信号から 空間周波数の異なる特定パターンを重み付けして発生させる演算回路と、画像信 号を発生する画像発生装置とを備えた表示装置を提案する。

[0016]

前記演算回路は、ブロック毎に画像信号から空間周波数の異なるn個の特定パ ターンを重み付けして発生させる手段であり、表示モジュールが、特定パターン をNp(nより小さい自然数)個加え合わせて画像を表示する手段である。

[0017]

また、特定パターンを加え合わせる個数Npを変更する手段として圧縮率調整 装置を備えることもできる。

[0018]

さらに、ブロックによって加え合わせる特定パターンの種類の数を変更する手 段として高圧縮演算回路を備えてもよい。

[0019]

本発明は、また、表示モジュールが、画素をマトリクス状に配列したパネルと 、信号ドライバと、走査ドライバと、対向信号ドライバとを備え、信号ドライバ には信号線を接続し、走査ドライバには走査線を接続し、対向信号ドライバには 対向信号線を接続し、画素が、信号電極と対向信号電極とスイッチ素子とを備え 、信号電極にはスイッチ素子を介して信号線を接続し、対向信号電極には対向信 号線を接続し、同一のブロックに含まれて同一の行の画素に備えられた信号電極 には同一の第1電位を与え、同一のブロックに含まれて同一の列の画素に備えら れた対向信号電極には同一の第2電位を与え、ブロックが第1電位と第2電位と により特定パターンを形成し、同一の行に含まれる画素に備えられた前期対向信 号電極には共通の対向信号線を接続した表示装置を提案する。

[0020]

本発明は、さらに、表示モジュールが、画素がマトリクス状に配列したパネル と、信号ドライバと、走査ドライバと、対向信号ドライバとを備え、信号ドライ バには信号線を接続し、走査ドライバには走査線を接続し、対向信号ドライバに は対向信号共通線を接続し、対向信号共通線には対向信号線を接続し、画素は信

出証特2000-3095497

号電極と対向信号電極とスイッチ素子とを備え、信号電極にはスイッチ素子を介 して信号線を接続し、対向信号電極には対向信号線を接続し、同一のブロックに 含まれて同一の行の画素に備えられた信号電極には同一の第1電位を与え、同一 のブロックに含まれて同一の列の画素に備えられた対向信号電極には同一の第2 電位を与え、ブロックが第1電位と第2電位とにより特定パターンを形成し、異 なるブロックに含まれる画素に備えられた対向信号電極には異なる対向信号線を 接続した表示装置を提案する。

[0021]

本発明は、表示モジュールが、画素がマトリクス状に配列したパネルと、信号 ドライバと、走査ドライバと、対向信号ドライバとを備え、信号ドライバには信 号線を接続し、走査ドライバには走査線を接続し、対向信号ドライバには対向信 号共通線を接続し、対向信号共通線には対向信号線を接続し、画素は信号電極と 対向信号電極とスイッチ素子とを備え、信号電極にはスイッチ素子を介して信号 線を接続し、対向信号電極には対向信号線を接続し、同一のブロックに含まれて 同一の行の画素に備えられた信号電極には同一の第1電位を与え、同一のブロッ クに含まれて同一の列の画素に備えられた対向信号電極には同一の第2電位を与 え、ブロックが第1電位と第2電位とにより特定パターンを形成し、異なるブロ ックに含まれる画素に備えられた対向信号電極には異なる対向信号線を接続し、 同一のブロックに含まれて異なる行の画素に備えられた対向信号電極にはそれぞ れ異なる対向信号線を接続した表示装置を提案する。

[0022]

ブロックの行方向の画素数は、ブロックの列方向の画素数よりも多いことがあ る。

[0023]

ブロックを形成する複数画素の組み合わせも、可変とすることができる。

[0024]

表示モジュールが、投射型ディスプレイであり、投射型ディスプレイが、特定 パターンを表示する投射パターン表示源と、パターン表示素子とを備え、パター ン表示素子が、透明電極が形成された一対の基板と透明電極上に形成された光導

出証特2000-3095497

電層と一対の基板に狭持された液晶層とを備える。

[0025]

表示モジュールは、特定パターンを順次表示し画像を加え合わせて表示する手 段として構成してもよい。

[0026]

表示モジュールは、また、特定パターンを画素内で演算し加え合わせて画像を 表示する手段とすることも可能である。

[0027]

この場合、表示モジュールは、画素をマトリクス状に配列したパネルと、信号 ドライバと、走査ドライバと、共通電極ドライバとを備え、信号ドライバには信 号線を接続し、走査ドライバには走査線を接続し、共通電極ドライバには共通電 極線を接続し、各画素には特定パターンを加え合わせる加減算器を備え、加減算 器には特定パターンを加え合わせる個数Npに等しい数の信号線を接続して形成 する。

[0028]

パネルは、より具体的には、画素に液晶を備えた液晶パネルであり、各画素に は信号線を介して送られる信号をホールドする容量素子を、特定パターンを加え 合わせる個数Np個以上備え、容量素子と液晶の容量とを結合する手段を備える

[0029]

画素を構成するそれぞれの回路が、デジタル信号のサンプルホールド手段と、 アナログ信号のサンプルホールド手段とを備えることができる。

[0030]

デジタル信号のサンプルホールド手段にホールドされた信号に応じて、アナロ グ信号のサンプルホールド手段にホールドされた信号を書き換え、同一のブロッ クに含まれる画素には、同一の信号を与えるようにする。

[0031]

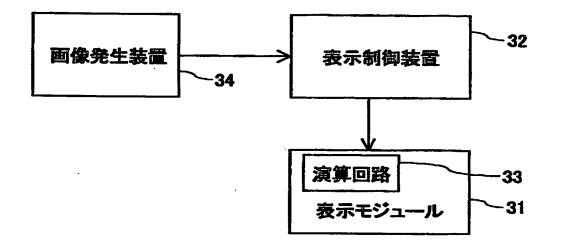

画像発生装置が、演算回路を含む場合もあり、表示制御装置が、演算回路を含む場合もあり、表示モジュールが、演算回路を有することもある。

1 1

出証特2000-3095497

[0032]

表示モジュールの代表的なものとしては、液晶モジュールがある。

[0033]

【発明の実施の形態】

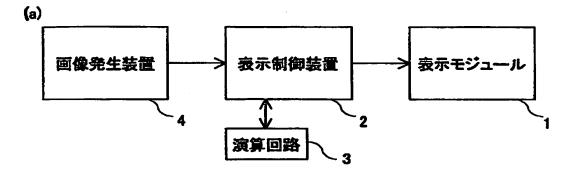

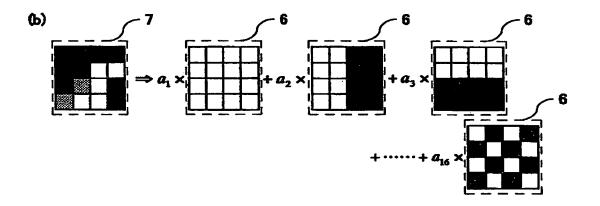

図1は、本発明による表示装置の全体構成を示すブロック図および動作原理を 示す図である。MPEG(Moving Picture Experts Group)やJPEG(Joint Pho tographic Experts Group)などの画像圧縮技術に利用されている直交変換を画像 に施すと、図1(b)に示すように、その画像の中のあるブロックが形成する画像 7は、種々の空間周波数成分を持つ特定パターン6の重み付き線形和で表現でき る。

[0034]

通常、画像には、空間相関があるため、空間周波数の低い特定パターンの重み が大きく、空間周波数の高い特定パターンの重みは、小さくなる。重みの小さい 特定パターンは、画像にとって重要な情報ではないため、その特定パターンを省 略しても画像に大きな影響を与えず、画像は、ほとんど劣化しない。この特性を 利用して、情報量を圧縮できる。

[0035]

例えば、行方向に $n_1$ 個の画素、列方向に $n_r$ 個の画素からなるブロックに直 交変換を施した場合は、 $n_1 \times n_r$ 個の特定パターンが存在するが、この特定パ ターンのうちNp個の特定パターンを用いて画像を再現できるとすると、1つの 特定パターンには、1つの重みの情報が対応するため、情報量がNp/( $n_1 \times n_r$ )に圧縮されたことになる。

[0036]

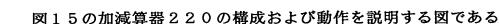

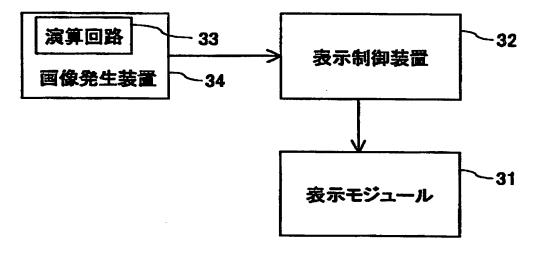

本発明の表示装置は、図1(a)に示すように、空間周波数の異なる特定パター ン6を1ないし複数個加え合わせて画像8を表示する(図1(c)参照)表示モジュ ール1と、表示モジュール1を制御する表示制御装置2と、ブロック毎に画像信 号7から空間周波数の異なる特定パターン6を重み付けして発生させる(図1(b) )参照)演算回路3と、画像信号7を発生する画像発生装置4とを備えている。本 発明の表示装置においては、重み付けされた空間周波数の異なる特定パターンを

表示装置上で加え合わせて画像を形成するため、信号クロック周波数f<sub>s</sub>は、以 下に説明するように減少する。

[0037]

$n_1 \times n_r$ の画素からなる1つのブロックが1つの特定パターンを形成すると きは、そのブロックには、1つの重み付けの信号が対応する。そのため、画素が 行方向に $n_{01}$ 個、列方向に $n_{0r}$ 個ある表示パネルには、 $(n_{01} \times n_{0r})/(n_1 \times n_r)$ 個の信号が必要となる。画像を再現するために、全ブロックがNP 個の特定パターンを必要とすると、表示モジュールには、1つの画像につきNP × $(n_{01} \times n_{0r})/(n_1 \times n_r)$ 個の信号が必要となる。この信号が周期1/ f<sub>H</sub>毎に必要となるため、信号クロック周波数f<sub>s</sub>は、数式3のようになる。

[0038]

【数3】

$$f_s = N_p \times \frac{n_{0l} \times n_{0r}}{n_l \times n_r} \times f_H = n_{0l} \times n_{0r} \times f_H \times \frac{N_p}{n_l \times n_r}$$

数式1と数式3とを比較すると、信号クロック周波数がNp/(n<sub>1</sub>×n<sub>r</sub>)倍 だけ減少していることが分かる。

[0039]

次に、データ信号書き込み時間 t<sub>s</sub>について考える。本発明では、行方向に n 1個、列方向に n<sub>r</sub> 個の画素からなるブロック単位で書き込むため、 n<sub>1</sub>行分の 画素をまとめて走査する。1つの画像を再現するために、この走査を Np回繰り 返して画像を再現するので、データ信号書き込み時間は、数式4のようになる。

[0040]

【数4】

$t_s = \frac{1}{f_m \times n_{ol}} \times \frac{n_l}{N_m}$

したがって、n<sub>1</sub>>Npのとき、データ信号書き込み時間が増大する。また、 本発明では、n<sub>1</sub>行分の画素をまとめて走査するため、複数の行で走査線を共有 でき、開口率を上げることができる。

[0041]

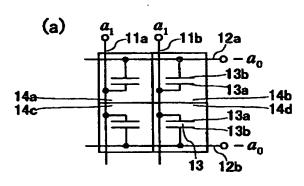

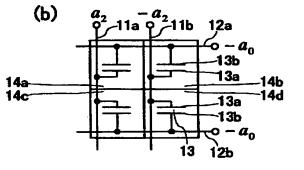

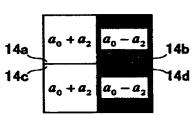

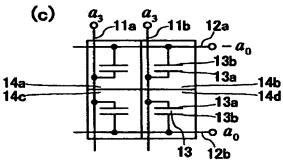

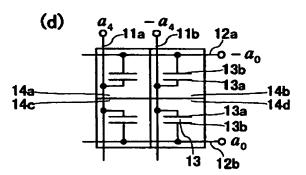

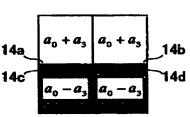

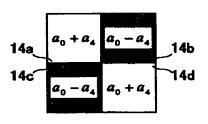

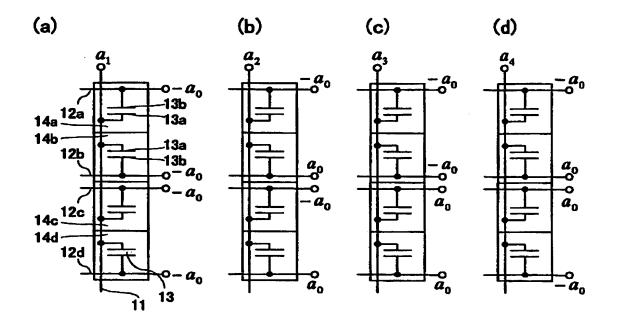

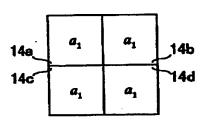

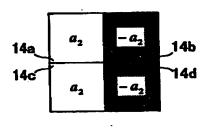

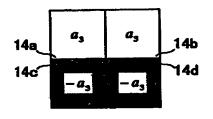

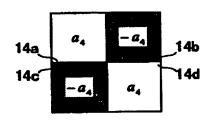

図4は、本発明により画素上で特定パターンを表示する原理を説明する図であ る。図4では、行方向に2個、列方向に2個、合計4個の画素14a,14b, 14c,14dを1つのブロックとして扱う場合が示されている。1つの画素に は、信号線11aまたは11bに接続された信号電極13aと、対向信号線12 aまたは12bに接続された対向信号電極13bとからなる画素電極13がある

[0042]

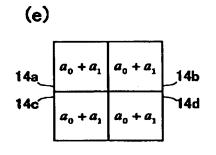

図4(a)に示すように、信号線11a, 11bに電圧 $a_1$ を印加し、対向信号線12a, 12bに電圧 $-a_0$ を印加すると、図4(e)に示すように、画素14 a, 14b, 14c, 14dの画素電極13には、絶対値が $a_0$ + $a_1$ の電圧が印加される。

[0043]

図4(b)に示すように、信号線11a, 11bにそれぞれ電圧 $a_2$ ,  $-a_2$ を 印加し、対向信号線12a, 12bにそれぞれ電圧 $-a_0$ ,  $-a_0$ を印加すると 、図4(f)に示すように、画素14a, 14b, 14c, 14dの画素電極13 には、それぞれ絶対値が $a_0$  +  $a_2$ ,  $a_0$  -  $a_2$ ,  $a_0$  +  $a_2$ ,  $a_0$  -  $a_2$ の電 圧が印加される。

【0044】

図4(c)に示すように、信号線11a, 11bにそれぞれ電圧 $a_3$ ,  $a_3$ を印 加し、対向信号線12a, 12bにそれぞれ電圧 $-a_0$ ,  $a_0$ を印加すると、図 4(g)に示すように、画素14a, 14b, 14c, 14dの画素電極13には 、それぞれ絶対値が $a_0$  +  $a_3$ ,  $a_0$  +  $a_3$ ,  $a_0$  -  $a_3$ ,  $a_0$  -  $a_3$ の電圧が 印加される。

[0045]

図4(d)に示すように、信号線11a, 11bにそれぞれ電圧 $a_4$ ,  $-a_4$ を

出証特2000-3095497

印加し、対向信号線12a, 12bにそれぞれ電圧 $-a_0$ ,  $a_0$ を印加すると、 図4(h)に示すように、画素14a, 14b, 14c, 14dの画素電極13に は、それぞれ絶対値が $a_0 + a_4$ ,  $a_0 - a_4$ ,  $a_0 - a_4$ ,  $a_0 + a_4$ の電圧 が印加される。

[0046]

ここで、画素電極13に印加される電圧の絶対値が $a_0 + a_j$ (j = 1, 2, 3, 4)である画素を白色、同じく $a_0 - a_j$ である画素を灰色として識別すると、 図4(e)ないし(h)が示すように、空間周波数の異なる特定パターンが表示でき ていることが分かる。

[0047]

本明細書では、便宜上、このようにして特定パターンを形成する方法を「特定 パターン表示法」と呼ぶことにする。

[0048]

次に、図1の演算回路3における空間周波数の異なる特定パターンの発生方法 と、表示モジュール1において空間周波数の異なる特定パターンを1ないし複数 個加え合わせる方法について、表示パネルとして液晶パネルを使用した液晶表示 装置を例にとって説明する。

[0049]

本発明は、空間相関を利用するため、近隣の画素で1ブロックを形成する。こ こでは、図4に示すように、行方向に2個,列方向に2個の2×2の画素を1ブ ロックとして説明する。

[0050]

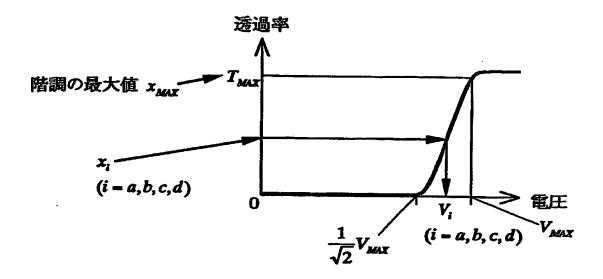

図5は、液晶に印加すべき電圧 $V_a$ ,  $V_b$ ,  $V_c$ ,  $V_d$ の決定の様子を示す図 である。はじめに、画像発生装置から送られてきた画素14a, 14b, 14c , 14dの階調信号 $x_a$ ,  $x_b$ ,  $x_c$ ,  $x_d$ より、液晶の透過率一電圧特性に基 づいて、液晶に印加すべき電圧 $V_a$ ,  $V_b$ ,  $V_c$ ,  $V_d$ を図5に示すように決定 する。この電圧を、便宜上ここでは、「目標電圧」と呼ぶ。

[0051]

次に、この「目標電圧」より、下記の計算によって、特定パターンの重み a j

[0052]

【数5】

$$\begin{cases} a_{1} = -a_{0} + \sqrt{\frac{N_{p}}{4} \sum_{i} V_{i}^{2} - 3a_{0}^{2} - \frac{N_{p}^{2}}{64a_{0}^{2}} \left\{ 4 \sum_{i} V_{i}^{4} - \left(\sum_{i} V_{i}^{2}\right)^{2} \right\}} \\ a_{2} = \frac{N_{p}}{8a_{0}} \left( V_{a}^{2} - V_{b}^{2} + V_{c}^{2} - V_{d}^{2} \right) \\ a_{3} = \frac{N_{p}}{8a_{0}} \left( V_{a}^{2} + V_{b}^{2} - V_{c}^{2} - V_{d}^{2} \right) \\ a_{4} = \frac{N_{p}}{8a_{0}} \left( V_{a}^{2} - V_{b}^{2} - V_{c}^{2} + V_{d}^{2} \right) \end{cases}$$

[0053]

【数6】

$a_0 = \sqrt{\frac{N_p}{8}V_{MAX}}$

V<sub>MAX</sub>は、図5に示すように、「目標電圧」の最大値である。例えば、液晶 パネルが図5に示すようなノーマリブラックの透過率-電圧特性を示す場合は、 階調信号の最大値×<sub>MAX</sub>に対応した透過率T<sub>MAX</sub>を与える電圧がV<sub>MAX</sub>で ある。T<sub>MAX</sub>は、透過率-電圧特性における最大透過率である必要はないが、 最大透過率に近いほど高い輝度が得られる。

[0054]

数式5は、直交変換の1つであるアダマール変換を模した変換であり、アダマ ール変換と同様に、空間周波数の異なる特定パターンの重み付けを実行できる。

[0055]

このようにして空間周波数の異なる特定パターンの重みを求める方法を、便宜

上、「擬似直交変換法」と呼ぶことにする。

「擬似直交変換法」によって求めた a j (j = 1,2,3,4)および a 0 を、図4 ですでに説明したように、「特定パターン表示法」によって画素内の電極に印加 すると、図4(e)ないし(h)が示すような空間周波数の異なる特定パターンを形 成できる。

[0056]

この特定パターンの1つ1つを、1つのフレームから分けられたサブフレーム に割り当て、フィールドシーケンシャル駆動方式で特定パターンを順次に表示し 、特定パターンを加え合わせる。

[0057]

具体的には、以下のように加え合わせる。4つの特定パターン全てをフィール ドシーケンシャル駆動方式で順次に表示すると、各画素の実効値電圧は、数式7 のようになる。

[0058]

【数7】

$$\begin{cases} V_{a}^{'} = \frac{1}{\sqrt{N_{p}}} \sqrt{(a_{0} + a_{1})^{2} + (a_{0} + a_{2})^{2} + (a_{0} + a_{3})^{2} + (a_{0} + a_{4})^{2}} \\ V_{b}^{'} = \frac{1}{\sqrt{N_{p}}} \sqrt{(a_{0} + a_{1})^{2} + (a_{0} - a_{2})^{2} + (a_{0} + a_{3})^{2} + (a_{0} - a_{4})^{2}} \\ V_{c}^{'} = \frac{1}{\sqrt{N_{p}}} \sqrt{(a_{0} + a_{1})^{2} + (a_{0} + a_{2})^{2} + (a_{0} - a_{3})^{2} + (a_{0} - a_{4})^{2}} \\ V_{d}^{'} = \frac{1}{\sqrt{N_{p}}} \sqrt{(a_{0} + a_{1})^{2} + (a_{0} - a_{2})^{2} + (a_{0} - a_{3})^{2} + (a_{0} + a_{4})^{2}} \end{cases}$$

ただし、Np=4である。数式7に数式5および数式6を代入すると、V<sub>a</sub>' =V<sub>a</sub>, V<sub>b</sub>'=V<sub>b</sub>, V<sub>c</sub>'=V<sub>c</sub>, V<sub>d</sub>'=V<sub>d</sub>となり、「目標電圧」に等 しい電圧を印加できる。すなわち、特定パターンをフィールドシーケンシャル駆 動方式で表示すると、原画像を再現できる。

[0059]

数式5による重み付けの結果、 $a_2 \ge a_4 m a_1 \ge a_3$ に比べて十分に小さい とき、 $a_2$ に対応する特定パターン(図4(f))と、 $a_4$ に対応する特定パターン (図4(h))を省略しても画像に大きな影響を与えない。

[0060]

そこで、a2に対応する特定パターンとa4に対応する特定パターンとを省略 したとき、各画素の実効値電圧は、数式8のようになる。

[0061]

【数 8】

$$\begin{cases} V_{a}' = \frac{1}{\sqrt{N_{p}}} \sqrt{(a_{0} + a_{1})^{2} + (a_{0} + a_{3})^{2}} \cong V_{a} \\ V_{b}' = \frac{1}{\sqrt{N_{p}}} \sqrt{(a_{0} + a_{1})^{2} + (a_{0} + a_{3})^{2}} \cong V_{b} \\ V_{c}' = \frac{1}{\sqrt{N_{p}}} \sqrt{(a_{0} + a_{1})^{2} + (a_{0} - a_{3})^{2}} \cong V_{c} \\ V_{d}' = \frac{1}{\sqrt{N_{p}}} \sqrt{(a_{0} + a_{1})^{2} + (a_{0} - a_{3})^{2}} \cong V_{d} \end{cases}$$

ただし、Np=2である。このように、4つの画素に対して、2つの特定パタ ーンの加え合わせで表示すると、信号クロックは、半分に減少できる。

[0062]

ここでは、 a<sub>1</sub>と a<sub>3</sub>とに対応する特定パターンをフィールドシーケンシャル 駆動方式で表示することを例としてあげたが、重みの大きい特定パターンをフィ ールドシーケンシャル駆動方式で表示することで、原画像に近い画像を表示でき る。

【0063】

ところで、数式5において適切な重み付けを実行できるように、 $a_1 > 0$ を条件とすると、 $V_i > V_{MAX} / \sqrt{2}$  (i = a, b, c, d)でなければならない。

出証特2000-3095497

また、特定パターンを形成するためには、 a $_0$ > a $_j$ である必要があるが、この 条件より、 V $_i$  < V $_{MAX}$ が要求される。すなわち、数式9を満たす必要がある

[0064]

【数9】

## $V_{\rm max}/\sqrt{2} < V_i < V_{\rm MAX}$

以上のように、各ブロック毎に「擬似直交変換法」によって空間周波数の異な る特定パターンの重みを求め、「特定パターン表示法」によって大きな重みを持 つ特定パターンをフィールドシーケンシャル駆動方式で表示し画像を表示する方 法を、便宜上、「擬似直交変換表示法」と呼ぶ。

[0065]

この「擬似直交変換表示法」によって信号クロック周波数を低下させ、やデー タ信号書き込み時間の増大を実現し、高精細かつ高速駆動可能な表示装置を提供 できる。

[0066]

【実施形態1】

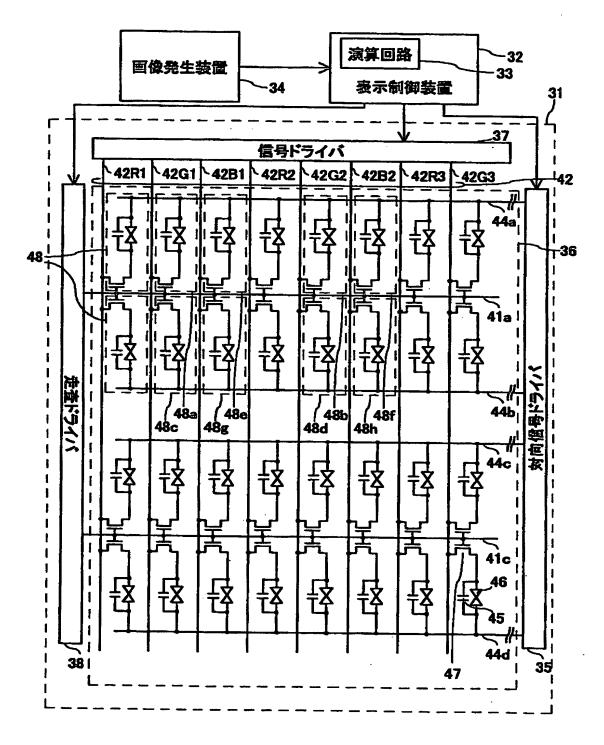

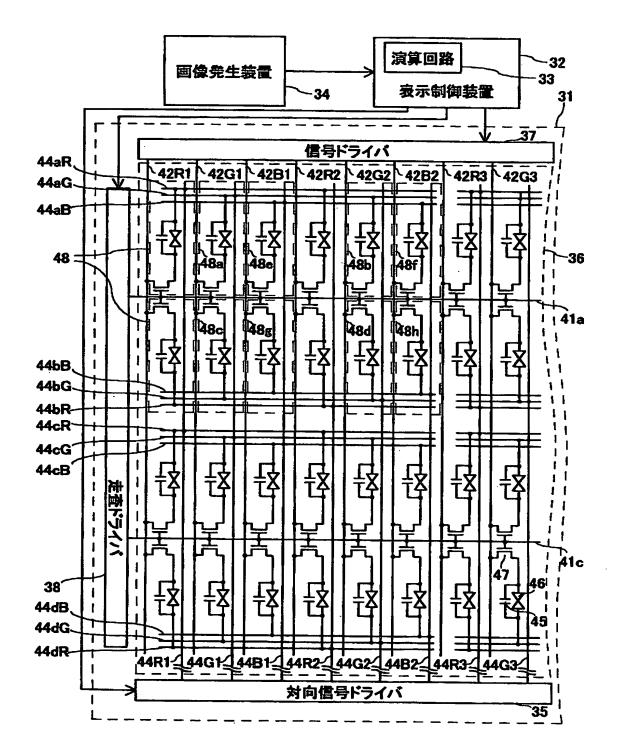

図6は、本発明による表示装置の実施形態1の構成を示す図である。本実施形 態1の表示装置は、表示パネル36として液晶パネルを用いた液晶表示装置であ る。

[0067]

本実施形態1の液晶表示装置は、図6に示すように、複数画素を1ブロック単 位としブロック単位中の複数画素を同時に選択し、空間周波数の異なる特定パタ ーンを1ないし複数個加え合わせて画像を表示する表示モジュール31と、表示 モジュール31を制御する表示制御装置32と、ブロック毎に画像信号から空間 周波数の異なる特定パターンを重み付けして発生させる演算回路33と、画像信 号を発生する画像発生装置34とを備えている。表示モジュール31は、画素4 8がマトリクス状に配列した液晶パネル36と、信号ドライバ37と、走査ドラ

イバ38と、対向信号ドライバ35とを含んでいる。

[0068]

信号ドライバ37には、信号線42が接続され、走査ドライバ38には、走査 線41a,41c,…が接続され、対向信号ドライバ35には、対向信号線44 a,44b,44c,44d,…が接続されている。

[0069]

画素48には、薄膜トランジスタ(TFT)47と、容量素子45と、液晶46 に電圧を印加するための信号電極(図示せず)および対向信号電極(図示せず)とが 備えられており、信号電極は、TFT47を介して、信号線42に接続され、対 向信号電極は、対向信号線44a,44b,44c,44d,…のいずれかに接 続されている。

[0070]

また、列方向に順に、赤色(R)を呈する画素と緑色(G)を呈する画素と青色( B)を呈する画素とが並んでいる。すなわち、信号線42R1,42R2,42 R3,…のいずれかに接続された画素は、R画素であり、信号線42G1,42 G2,42G3,…のいずれかに接続された画素は、G画素であり、信号線42 B1,42B2,…のいずれかに接続された画素は、B画素である。

[0071]

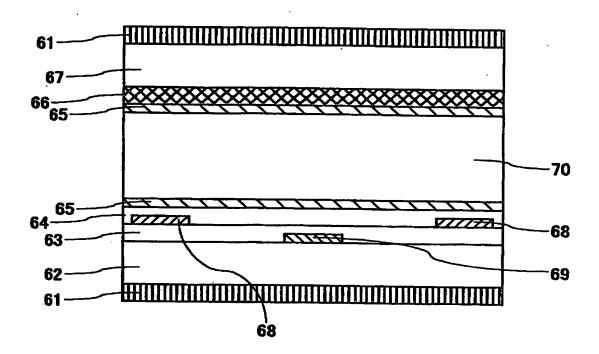

図7は、本実施形態1の液晶パネルの構成を説明する画素部分の断面構造を示 す図である。液晶パネルは、信号電極68と対向信号電極69と絶縁膜63,6 4と配向膜65とを備えた基板62と、基板62に対向配置されカラーフィルタ 66と配向膜65とを備えた基板67と、基板62と基板67とに挟まれた液晶 70と、基板62および基板67の液晶70に面しない面上に形成された偏光板 61とからなる。

[0072]

基板62および基板67としては、厚みが0.7mmのガラス基板を使用した 。基板62上には、アモルファスシリコンを用いてTFT(図示せず)を作製した 。信号電極68および対向信号電極69には、クロムモリブデン(CrMo)を使 用した。絶縁膜63,64は、窒化珪素からなり、膜厚をそれぞれ0.2μm,

○.8µmとした。画素数は、1280×3×1024個とした。配向膜65は、膜厚を80nmとし、その表面には、液晶を配向させるためのラビング処理を施した。

[0073]

図6の演算回路33では、以下に説明するようにして、空間周波数の異なる特 定パターンの重み付けを実行し、加え合わせる特定パターンを選択した。

[0074]

本発明は、空間相関を利用するため、R画素とG画素とB画素とは、それぞれ 独立に処理する必要がある。また、R画素,G画素,B画素のそれぞれにおいて は、近隣の複数画素でブロックを形成し、その複数画素の空間相関を利用する。

[0075]

したがって、図6において、画素48a,48b,48c,48dの行方向に 2個、列方向に2個の2×2の画素を1ブロックとした。同様にして、画素48 e,48f,48g,48hを1ブロックとした。以下同様にして、全ての画素 をブロック単位で扱った。

[0076]

各ブロック毎に、すでに説明した「擬似直交変換法」によって、図4(e)ない し(h)に示した4つの特定パターンの重み付けを実行した。

その4つの特定パターンのうち、加え合わせる特定パターンとして3つを選択した。

[0077]

このとき、図6に示すように、同一の行にある全ての画素48は、対向信号線 44a,44b,44c,44dのいずれか1本に接続されており、その画素の 対向信号電極には、全て同一の電圧が供給される。

したがって、例えば、対向信号線44a,44bにそれぞれ、 $-a_0$ , $-a_0$ を 印加すると、対向信号線44a,44bが接続されている2行に含まれるブロッ クが表示できる特定パターンは、図4(e)および(f)のみである。

[0078]

同様に、対向信号線44a,44bにそれぞれ、-a<sub>0</sub>,a<sub>0</sub>を印加すると、

出証特2000-3095497

表示できる特定パターンは、図4(g)および(h)のみである。

したがって、図4(e)または(f)と図4(g)または(h)とは、同じ行に含まれる ブロックでは、同時に表示できない。

[0079]

そのため、4つの特定パターンのうち3つを選択する際には、ほとんどのブロックで重みが最小となる空間周波数の最も高い特定パターンである図4(h)以外の3つの特定パターン図4(e)ないし(g)を選択した。

[0080]

選択された3つの特定パターンを図6における表示制御装置32で制御し、表 示モジュール31に備えられた液晶パネル36上でフィールドシーケンシャル駆 動方式で表示した。

[0081]

例えば、図4(e)ないし(g)に示した特定パターンの重みがそれぞれ、画素4 8 a, 4 8 b, 4 8 c, 4 8 dからなるブロックでは、 $a_1'$ ,  $a_2'$ ,  $a_3'$ であり、画素4 8 e, 4 8 f, 4 8 g, 4 8 hからなるブロックでは、 $a_1''$ ,  $a_2''$ ,  $a_3''$ であるとする。

[0082]

図6における走査線41 aにアドレス信号が与えられ、画素48a,48b, 48c,48dからなるブロックを含む2行が選択されているとき、信号線42 G1,42G2には、それぞれ、 $a_1$ ', $a_1$ 'の電圧を供給し、信号線42B 1,42B2には、それぞれ、 $a_1$ ", $a_1$ "の電圧を供給し、対向信号線44 a,44bには、それぞれ、 $-a_0$ ,  $-a_0$ の電圧を供給すると、画素48a, 48b,48c,48dの液晶に印加される電圧は、全て $a_0$ + $a_1$ 'となって、この4つの画素からなるブロックは、図4(e)に示すような特定パターンを形成し、画素48e,48f,48g,48hの液晶に印加される電圧は、全て $a_0$ + $a_1$ "となって、この4つの画素からなるブロックは、図4(e)に示すよう な特定パターンを形成する。

[0083]

同様に、走査線41aによって選択されている全てのブロックは、図4(e)な

22

出証特2000-3095497

いし(f)に示すような特定パターンのいずれかを形成する。

[0084]

次に、走査線41cにアドレス信号が与えられ、選択された2行に含まれるブ ロックは、同様に特定パターンを形成する。

[0085]

以下同様にして、走査する。

[0086]

全走査線の走査が終了し、再び走査線41aにアドレス信号が与えられ、画素 48a,48b,48c,48dからなるブロックを含む2行が選択されている とき、信号線42G1,42G2には、それぞれ、a<sub>2</sub>', -a<sub>2</sub>'の電圧を供 給し、信号線42B1,42B2には、それぞれ、a<sub>2</sub>", -a<sub>2</sub>"の電圧を供 給し、対向信号線44a,44bには、それぞれ、-a<sub>0</sub>, -a<sub>0</sub>の電圧を供給 すると、画素48a,48b,48c,48dの液晶に印加される電圧は、それ ぞれ、a<sub>0</sub>+a<sub>2</sub>', a<sub>0</sub>-a<sub>2</sub>', a<sub>0</sub>+a<sub>2</sub>', a<sub>0</sub>-a<sub>2</sub>'となって、こ の4つの画素からなるブロックは、図4(f)に示すような特定パターンを形成し 、画素48e,48f,48g,48hの液晶に印加される電圧は、それぞれ、  $a_0+a_2$ ",  $a_0-a_2$ ",  $a_0+a_2$ ",  $a_0-a_2$ "となって、この4つ の画素からなるブロックは、図4(f)に示すような特定パターンを形成し

[0087]

-,-\*

同様にして、全走査線を走査し、再び走査線41aにアドレス信号が与えられ たとき、同様に信号を供給すると、選択されたブロックは、図4(g)に示すよう な特定パターンを形成する。

[0088]

このように、「特定パターン表示法」に従い、各ブロックに特定パターンを形 成する電圧を与え、これをフィールドシーケンシャル駆動方式と組み合わせるこ とにより、電圧の実効値は、「目標電圧」に近く、画像発生装置が発生させた画 像とほぼ同様の画像を表示できた。

[0089]

このとき、4つの画素に対して、3つの特定パターンを加え合わせることによ

って表示したので、数式1と数式3との比較から分かるように、図3に示す線順 次走査駆動法の場合に比べ、信号クロック周波数を3/4に減少させることがで きた。

[0090]

また、走査線を、2行で共有しているため、図3に示す線順次駆動法の場合に 比べ、開口率も向上した。

[0091]

【実施形態2】

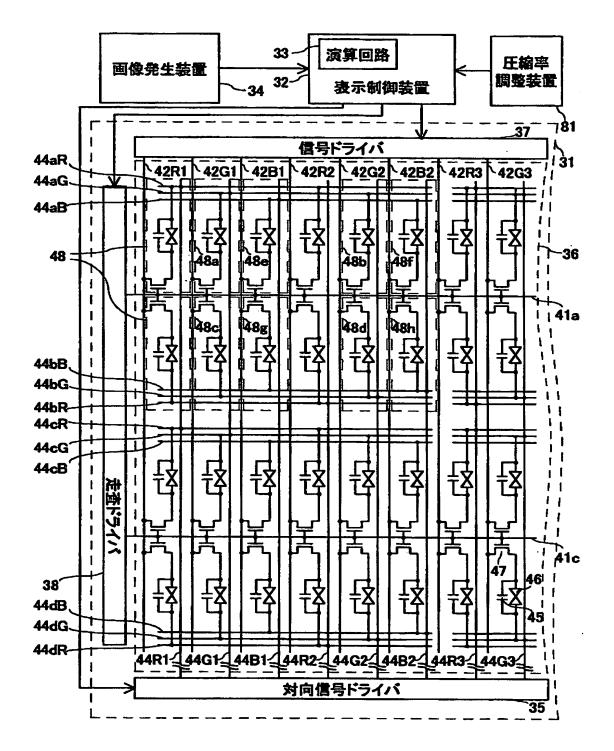

図8は、本発明による表示装置の実施形態2の構成を示す図である。本実施形 態2の表示装置は、表示パネル36として液晶パネルを用いた液晶表示装置であ る。

[0092]

本実施形態の液晶表示装置は、図8に示すように、画素48がマトリクス状に 配列した液晶パネル36と信号ドライバ37と走査ドライバ38と対向信号ドラ イバ35とを備え、複数画素を1ブロック単位とし、ブロック単位中の複数画素 を同時に選択し、空間周波数の異なる特定パターンを1ないし複数個加え合わせ て画像を表示する表示モジュール31と、表示モジュール31を制御する表示制 御装置32と、ブロック毎に画像信号から空間周波数の異なる特定パターンを重 み付けして発生させる演算回路33と、画像信号を発生する画像発生装置34と を備えている。

[0093]

信号ドライバ37には、信号線42R1,42G1,42B1,42R2,… が接続され、走査ドライバ38には、走査線41a,41c,…が接続され、対 向信号ドライバ35には、対向信号共通線44R1,44G1,44B1,44 R2,…が接続されている。

[0094]

画素48には、TFT47と容量素子45と液晶46に電圧を印加するための 信号電極(図示せず)および対向信号電極(図示せず)とが備えられており、信号電 極は、TFT47を介して信号線42R1,42G1,42B1,42R2,…

出証特2000-3095497

のいずれかに接続され、対向信号電極は、対向信号線44aR,44aG,44 aB,44bR,44bG,44bB,44cR,…のいずれかに接続されてい る。

[0095]

対向信号線44aR,44aG,44aB,44bR,44bG,44bB, 44cR,…は、それぞれ、対向信号共通線44R1,44G1,44B1,4 4R2,…のいずれかに接続されている。

[0096]

また、列方向に順に、R画素とG画素とB画素とが並んでいる。

[0097]

本発明は、空間相関を利用するため、R画素とG画素とB画素とは、それぞれ 独立に処理する必要があり、また、R画素,G画素,B画素のそれぞれにおいて は、近隣の複数画素でブロックをする。

[0098]

そのため、画素48a,48b,48c,48dの2×2の画素を1ブロック とし、同様に、画素48e,48f,48g,48hを1ブロックとし、以下同 様にして、全ての画素をブロック単位で扱った。

[0099]

ここで、同じ行かつ同じブロックに属する画素48aの液晶と画素48bの液 晶のみが共通の対向信号線44aGに接続されている。すなわち、各ブロック毎 に対向信号線が独立に配線されている。

[0100]

この点において、実施形態2は、同じ行の全ての画素に共通の対向信号線を配 線した実施形態1と大きく異なる。

[0101]

本実施形態2の画素部分の断面図は、図7に示すように、実施形態1に同じで あるため説明を省略する。

[0102]

図8の演算回路33では、以下に説明するようにして、空間周波数の異なる特

25

出証特2000-3095497

定パターンの重み付けを実行し、特定パターンを選択した。

[0103]

各ブロック毎に、すでに説明した「擬似直交変換法」によって、図4(e)ない し(h)に示した4つの特定パターンの重み付けを実行した。

その4つの特定パターンのうち、重みの大きい2つを選択した。

[0104]

ここで、本実施形態2では、実施形態1と異なり、各ブロック毎に対向信号線 が用意されているため、図4(e)ないし(h)に示すような全ての特定パターンを 、同じ行に含まれるブロックにおいても同時に表示できる。

[0105]

そのため、実施形態1では、3つの特定パターンを選択したが、本実施形態2 では、2つのみの特定パターンを加え合わせることによって、同様の画質で画像 を表示できる。

[0106]

選択した2つの特定パターンを、図8における表示制御装置32で制御し、表 示モジュール31に備えられた液晶パネル36上でフィールドシーケンシャル駆 動方式で表示した。

[0107]

この方法は、実施形態1と同様であるため、一例を簡単に取り上げ説明する。 例えば、画素48a,48b,48c,48dからなるブロックにおいて、図4 (e)および(f)に示すような特定パターンの重みが他の2つの特定パターンの重 みより大きく、その重みがそれぞれa<sub>1</sub>'およびa<sub>2</sub>'とする。

[0108]

図8における走査線41 aにアドレス信号が与えられ、画素48a,48b, 48c,48dからなるブロックを含む2行が選択されているとき、信号線42 G1,42G2には、それぞれ $a_1$ ', $a_1$ 'の電圧を供給し、対向信号共通線 44G1,44G2には、それぞれ $-a_0$ , $-a_0$ の電圧を供給すると、画素4 8a,48b,48c,48dの液晶に印加される電圧は、全て $a_0$ + $a_1$ 'と なって、この4つの画素からなるブロックは、図4(e)に示すような特定パター

ンを形成する。

[0109]

同様に、走査線41aによって選択されている全てのブロックは、図4(e)ないし(h)に示すような特定パターンのいずれかを形成する。

[0110]

同様にして、全走査線の走査が終了し、再び走査線41aにアドレス信号が与 えられたとき、同様に適切に電圧を供給することによって、画素48a,48b ,48c,48dの液晶に印加される電圧は、それぞれ、 $a_0 + a_2'$ , $a_0 - a_2'$ , $a_0 + a_2'$ , $a_0 - a_2'$ となって、この4つの画素からなるブロッ クは、図4(f)に示すような特定パターンを形成する。

[0111]

このように、「特定パターン表示法」に従い、各ブロックに特定パターンを形 成する電圧を与え、これをフィールドシーケンシャル駆動方式と組み合わせるこ とにより、電圧の実効値は、「目標電圧」に近く、画像発生装置が発生させた画 像とほぼ同様の画像を表示できた。

[0112]

このとき、4つの画素に対して、2つの特定パターンを加え合わせることによって表示したので、数式1と数式3との比較から分かるように、図3に示す線順 次走査駆動法の場合に比べ、信号クロック周波数を半分に減少させることができた。

[0113]

なお、本実施形態2では、2×2の画素を1つのブロックとして取り扱ったが 、ブロックが4×4や8×8の画素からなる場合についても、本質的に何ら変わ らない。

[0114]

例えば、4×4の画素を1つのブロックとした場合、16個の特定パターンが 生じるが、そのうち8個程度のパターンを選択すれば、画質の劣化がなく、画像 を表示できる。

[0115]

この場合も、16個の画素に対して、8個の特定パターンを加え合わせて表示 するので、信号クロック周波数は、線順次駆動走査法に比べ、半分に低下する。

[0116]

【実施形態3】

図9は、本発明による表示装置の実施形態3の構成を示す図である。本発明に よる実施形態3は、図9に示すように、圧縮率調整装置81が加えられた以外は 、実施形態2に同じである。

[0117]

したがって、圧縮率調整装置81の機能について説明する。

[0118]

実施形態2では、特定パターンを加え合わせる個数Npが2に固定されていた が、本実施形態3の圧縮率調整装置81は、特定パターンを加え合わせる個数N pを可変とする機能を持つ。

[0119]

例えば、「擬似直交変換法」によって、あるブロックの特定パターンの重みが  $a_1 > a_3 > a_2 > a_4$ であったとする。ここで、Np=3の場合は、1つのフ レームを3つのサブフレームに分け、 $a_1$ ,  $a_3$ ,  $a_2$ のそれぞれに対応する特 定パターンを順次表示する。または、Np=1の場合は、1つのフレームで、 $a_1$ に対応する特定パターンを表示する。

[0120]

サブフレームの数は、加え合わせる特定パターン数Npによって変化するため、それに応じて走査ドライバ38が走査周波数を調整し、対応する。

[0121]

例えば、加え合わせる特定パターン数Npが増大すれば、サブフレームも増大 するため、走査周波数を増大させて対応する。

[0122]

また、数式6が示すように、対向信号線44aR,44aG,44aB,44

bR,44bG,44bB,44cR,…に与える電圧a<sub>0</sub>も特定パターン数N

pによって変化するので、それに応じて、対向信号ドライバ35が電圧a<sub>0</sub>を調

整し、対応する。

[0123]

以上に説明したように、圧縮率調整装置81によって特定パターンを加え合わ せる個数Npを可変とすることにより、Npの少ない低信号クロック周波数モード 、すなわち低消費電力モードと、Npの多い高画質モードとをユーザが選択可能 な液晶表示装置を提供できる。

[0124]

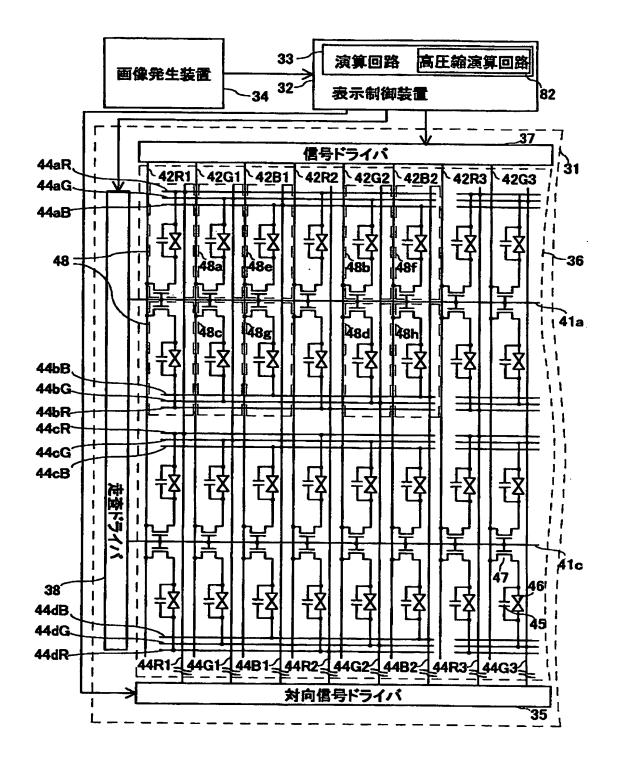

【実施形態4】

図10は、本発明による表示装置の実施形態4の構成を示す図である。本発明 による実施形態4は、図10に示すように、高圧縮演算回路82が加えられた以 外は、実施形態2に同じである。

[0125]

高圧縮演算回路82の機能について説明する。人の眼は、赤色や緑色の解像度 に比べて、青色の解像度に対して敏感ではないため、B画素において加え合わせ る特定パターンの種類をR画素やG画素における特定パターンの種類より少なく しても、画質の劣化を感じにくい。

[0126]

そのため、R画素やG画素からなるブロックについては、2種類の特定パター ンを表示したのに対し、B画素からなるブロックについては、図4(e)に示す特 定パターンのみを表示した。

[0127]

これにより、B画素からなるブロックについては、「擬似直交変換法」の数式 5においてa<sub>1</sub>のみを求めれば良く、演算が簡単化される。高圧縮演算回路82 が、この演算を担当し、演算回路33の負担を軽減できる。

[0128]

ただし、加え合わせる特定パターン数Npをブロック毎に変化させることはで きない。なぜなら、Npによってサブフレーム数が変化するが、同じ行に含まれ るブロックは、走査線41a,41c,…が共通であるため、ブロックによって 走査周波数を変化させることはできない。

[0129]

そのため、R画素およびG画素からなるブロックの加え合わせる特定パターン 数Npに合わせ、B画素からなるブロックでは、図4(e)に示す特定パターンを 2回表示した。

[0130]

以上のように、ブロックによって、加え合わせる特定パターンの種類の数が可 変となる演算回路を持つと、B画素からなるブロックでは、図4(e)に示すよう な特定パターンのみを表示でき、演算回路33の負担を軽減できる。

[0131]

【実施形態5】

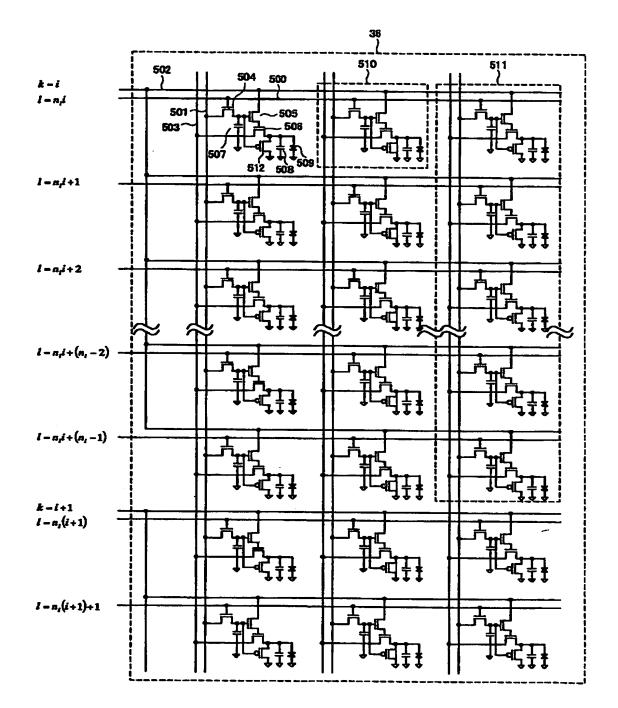

図11は、本発明による表示装置の実施形態5の構成を示す図である。本実 施形態5の表示装置は、表示パネル36として液晶パネルを用いた液晶表示装置 である。

[0132]

本実施形態5の液晶表示装置は、図11に示すように、画素48がマトリクス 状に配列した液晶パネル36と、信号ドライバ37と、走査ドライバ38と、対 向信号ドライバ35とを備え、複数画素を1ブロック単位とし、ブロック単位中 の複数画素を同時に選択し、空間周波数の異なる特定パターンを1ないし複数個 加え合わせて画像を表示する表示モジュール31と、表示モジュール31を制御 する表示制御装置32と、ブロック毎に画像信号から空間周波数の異なる特定パ ターンを重み付けして発生させる演算回路33と、画像信号を発生する画像発生 装置34とを備えている。

[0133]

信号ドライバ37には、信号線42R1,42G1,42B1,42R2,… が接続され、走査ドライバ38には、走査線41a,41c,41e,…が接続 され、対向信号ドライバ35には、対向信号共通線44が接続されている。

[0134]

画素48には、TFT47と、容量素子45と、液晶46に電圧を印加するた めの図示しない信号電極および対向信号電極とが備えられており、信号電極は、

出証特2000-3095497

**TFT47を介して、信号線42R1,42G1,42B1,42R2,…のいずれかに接続され、対向信号電極は、対向信号線44'に接続されている。対向** 信号線44'は、対向信号共通線44に接続されている。

[0135]

また、列方向に順に、R画素とG画素とB画素とが並んでいる。

[0136]

本発明は、空間相関を利用するため、R画素とG画素とB画素とは、それぞれ 独立に処理する必要があり、また、R画素,G画素,B画素のそれぞれにおいて は、近隣の複数画素で1ブロックを構成する。

[0137]

本実施形態5では、例えば、画素48a,48b,48c,48dからなるブ ロックのように、行方向に4個,列方向に1個の4×1の画素を1ブロックとし た。この1ブロックの構成は、2×2の画素を1ブロックとした実施形態2とは 異なる。

[0138]

4×1のブロック内の各画素には、それぞれ独立して対向信号線44'が配線 され、それぞれの対向信号線44'は、それぞれ独立して対向信号共通線44に 接続され、各画素にそれぞれ独立した対向信号電圧を供給できる。

[0139]

本実施形態5の画素部分の断面図は、図7に示すように、実施形態1に同じで あるため説明を省略する。

[0140]

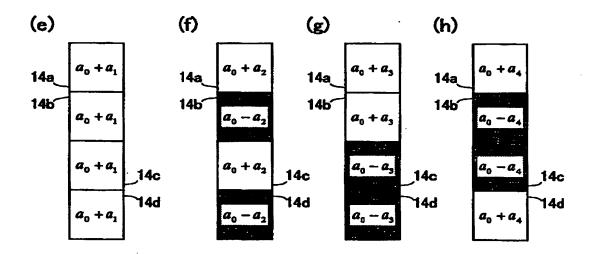

図12は、4×1のブロックにおいて特定パターンを表示する原理を説明する 図である。図12では、行方向に4個、列方向に1個、合計4つの画素14aお よび14bおよび14cおよび14dを1つのブロックとして扱う場合が示され ている。

[0141]

1つの画素には、信号線11に接続された信号電極13aと、対向信号線12 a, 12b, 12c, 12dのいずれかに接続された対向信号電極13bとから

なる画素電極13がある。

[0142]

1

図12(a)に示すように、信号線11に電圧 a<sub>1</sub>を印加し、対向信号線12a , 12b, 12c, 12dに電圧 – a<sub>0</sub>を印加すると、図12(e)に示すように 、画素14a, 14b, 14c, 14dの画素電極13には、絶対値が a<sub>0</sub>+a <sub>1</sub>の電圧が印加される。

[0143]

図12(b)に示すように、信号線11に電圧 $a_2$ を印加し、対向信号線12a, 12b, 12c, 12dにそれぞれ電圧 $-a_0$ ,  $a_0$ ,  $-a_0$ ,  $a_0$ を印加す ると、図12(f)に示すように、画素14a, 14b, 14c, 14dの画素電 極13には、絶対値がそれぞれ $a_0$  +  $a_2$ ,  $a_0$  -  $a_2$ ,  $a_0$  +  $a_2$ ,  $a_0$  -  $a_3$ , a

[0144]

図12(c)に示すように、信号線11に電圧 $a_3$ を印加し、対向信号線12a, 12b, 12c, 12dにそれぞれ電圧 $-a_0$ ,  $-a_0$ ,  $a_0$ ,  $a_0$ を印加すると、図12(g)に示すように、画素14a, 14b, 14c, 14dの画素電極13には、絶対値がそれぞれ $a_0$  +  $a_3$ ,  $a_0$  +  $a_3$ ,  $a_0$  -  $a_0$ ,  $a_0$

[0145]

図12(d)に示すように、信号線11に電圧 $a_4$ を印加し、対向信号線12a, 12b, 12c, 12dにそれぞれ電圧 $-a_0$ ,  $a_0$ ,  $a_0$ ,  $-a_0$ を印加す ると、図12(h)に示すように、画素14a, 14b, 14c, 14dの画素電 極13には、絶対値がそれぞれ $a_0 + a_4$ ,  $a_0 - a_4$ ,  $a_0 - a_4$ ,  $a_0 + a_4$  $_4$ の電圧が印加される。

[0146]

ここで、画素電極13に印加される電圧の絶対値が $a_0 + a_j$ (j = 1, 2, 3, 4)である画素を白色、同じく $a_0 - a_j$ である画素を灰色として識別すると、 図12(e)ないし(h)が示すように、空間周波数の異なる特定パターンが表示で きていることが分かる。

出証特2000-3095497

[0147]

図11の演算回路33では、以下に説明するようにして、空間周波数の異なる 特定パターンの重み付けを実行し、特定パターンを選択した。各ブロック毎に、 すでに説明した「擬似直交変換法」によって、図12(e)ないし(h)に示した4 つの特定パターンの重み付けを実行した。

[0148]

その4つの特定パターンのうち、重みの大きい3つを選択した。選択した3つ の特定パターンを、図11における表示制御装置32で制御し、表示モジュール 31に備えられた液晶パネル36上でフィールドシーケンシャル駆動方式で表示 した。

[0149]

この方法は、実施形態1と同様であるため、一例を簡単に取り上げ説明する。 例えば、画素4 8 a, 4 8 b, 4 8 c, 4 8 d からなるブロックにおいて、図1 2(e)および(g)および(h)の重みが他の特定パターンのそれより大きく、その 重みがそれぞれ  $a_1$  ' および  $a_3$  ' および  $a_4$  ' とする。

[0150]

図11における走査線41aおよび41cの2本の走査線に同時にアドレス信 号が与えられ、画素48a,48b,48c,48dからなるブロックを含む4 行が選択されているとき、信号線42G1にa<sub>1</sub>′の電圧を供給し、対向信号共 通線44G1a,44G1b,44G1c,44G1dには、それぞれ-a<sub>0</sub>,  $-a_0, -a_0, -a_0$ の電圧を供給すると、画素48a,48b,48c,4 8dの液晶に印加される電圧は、全て $a_0 + a_1'$ となって、この4つの画素か らなるブロックは、図12(e)に示すような特定パターンを形成する。

[0151]

同様に、走査線41aおよび41cによって選択されている全てのブロックは 、図12(e)ないし(h)に示すような特定パターンのいずれかを形成する。

[0152]

同様にして、全走査線の走査が終了し、再び走査線41aおよび41cにアド レス信号が与えられたとき、同様に適切に電圧を供給することによって、画素4

出証特2000-3095497

8 a, 4 8 b, 4 8 c, 4 8 dの液晶に印加される電圧は、それぞれ $a_0 + a_3$ ',  $a_0 + a_3$ ',  $a_0 - a_3$ ',  $a_0 - a_3$ ' となって、この4つの画素から なるブロックは、図1 2 (g)に示すような特定パターンを形成する。

[0153]

同様にして、全走査線の走査が終了し、再び走査線41aおよび41cにアド レス信号が与えられたとき、図12(h)に示すような特定パターンを形成する。

[0154]

このように、「特定パターン表示法」に従い、各ブロックに特定パターンを形 成する電圧を与え、これをフィールドシーケンシャル駆動方式と組み合わせると 、電圧の実効値は、「目標電圧」に近く、画像発生装置が発生させた画像とほぼ 同様の画像を表示できた。

[0155]

このとき、4つの画素に対して、3つの特定パターンを加え合わせることによって表示したので、数式1と数式3との比較から分かるように、図3に示す線順 次走査駆動法の場合に比べ、信号クロック周波数を3/4に減少させることがで きた。

[0156]

同時に、4行毎に走査したのに対し、3つのサブフレームによって表示したの で、数式2と数式4との比較から分かるように、データ信号書き込み時間を4/ 3倍に増大させることができた。

[0157]

このように、ブロックの行方向の画素数を列方向の画素数より多くすることに よって、ブロックの行方向の画素数と列方向の画素数とが等しい場合に比べ、信 号クロック周波数の減少率(Np/(n<sub>1</sub>×n<sub>r</sub>))が同じ場合においても、データ 信号書き込み時間の増大の効果を得やすくなる。

[0158]

特に、本実施形態5のようにブロックの列方向の画素数が1個の場合は、 $n_1$ × $n_r = n_1$ となるため、加え合わせる特定パターン数Npがブロックを形成す る画素数より小さければ、数式2および数式4から分かるように、信号クロック

34

出証特2000-3095497

周波数の減少の効果と、データ信号書き込み時間の増大の効果とが同時に得られる。

[0159]

なお、図11に示した液晶パネル36においては、例えば、画素48aと48 bのように、共通の走査線および信号線に接続されている画素には、同一の信号 電圧を印加することになるが、対向信号電圧は、それぞれ独立に供給できる。

[0160]

そのため、本実施形態5では、4×1の画素を1つのブロックとして扱ったが、2×1のブロック,2×2のブロック,4×4のブロックなども可能である。

[0161]

例えば、2×2のブロックの場合、画素48e,48f,48g,48hを1 つのブロックとして扱い、走査線41aにアドレス信号が与えられ、画素48e ,48f,48g,48hからなるブロックを含む2行が選択されているとき、 信号線42R1,42R2にそれぞれa<sub>2</sub>,-a<sub>2</sub>の電圧を供給し、対向信号共 通線44R1a,44R1b,44R2a,44R2bに-a<sub>0</sub>の電圧を供給す ると、画素48e,48f,48g,48hの液晶に印加される電圧は、それぞ れa<sub>0</sub>+a<sub>2</sub>,a<sub>0</sub>-a<sub>2</sub>,a<sub>0</sub>+a<sub>2</sub>,a<sub>0</sub>-a<sub>2</sub>となって、この4つの画素 からなるブロックは、図4(f)に示すような特定パターンを形成する。

[0162]

このように2×2からなる画素を1つのブロックとして扱った場合にも特定パ ターンを表示でき、画像を表示できる。

[0163]

これにより、2×2のブロックと4×1のブロックというように、ブロックを 形成する画素数が同じ場合には、そのブロックをリアルタイムに変更できる。す なわち、画像によって、2×2のブロックとして扱うのか、4×1のブロックと して扱うのかを切り換えできる。

[0164]

通常、4×1のブロックの場合は、2×2のブロックの場合に比べて、画質の 劣化は大きいが、データ信号書き込み時間は増大できる。

[0165]

そのため、画質を優先するときは、2×2のブロックで扱えば良い。

[0166]

また、通常2×2のブロックで処理している場合、その2×2のブロック内の 画素に全て同じ信号を与え、その2×2のブロックを1つの画素とみなして処理 する場合には、4×4のブロックでの処理に切り換えることが可能である。

[0167]

なぜなら、4×4のブロック内に含まれる2×2のブロックには、同一の信号 を送るため、実質的には2×2のブロックの処理と等価なためである。

[0168]

これにより、通常は、2×2のブロックで処理し、全画面で動画を表示する場合のように解像度が低い画像を表示する場合には、上記のようにして4×4のブロックで処理することにより、効率良く対応できる。

[0169]

【実施形態6】

図13は、本発明による表示装置の実施形態6の構成を示す図である。本発明 による実施形態6は、図6における液晶パネル36を、図13に示される液晶パ ネルとした以外は、実施形態1と同じである。また、本実施形態6の画素部分の 断面図は、図7に示すように、実施形態1に同じであるため説明を省略する。た だし、ポリシリコンを用いてTFTを作製した。したがって、液晶パネル36の 構成と信号書き込みのタイミングについて説明する。

[0170]

ブロック511は、同一のアナログ信号走査線502およびアナログ信号線5 03に接続されたn<sub>1</sub>個の画素510からなる。画素510は、デジタル信号走 査線500およびデジタル信号線501に接続された第1トランジスタ504と 、第1容量素子507と、アナログ信号走査線502に接続された第2トランジ スタ505と、アナログ信号線503に接続された第3トランジスタ506と、 第2容量素子508と、液晶509と、第4トランジスタ512とからなる。

[0171]

出証特2000-3095497

第1トランジスタ,第2トランジスタ,第3トランジスタは、nチャネル型の MOSトランジスタであり、第4トランジスタは、pチャネル型のMOSトラン ジスタである。

[0172]

第1容量素子507および第2容量素子508は、図示しない共通配線との間 に形成されている。

[0173]

第1トランジスタ504は、デジタル信号走査線500により選択され、デジ タル信号線501の信号をサンプルし、第1容量素子507にホールドする。デ ジタル信号線501の信号は、基本的に2値であり、一方は、第2トランジスタ 505のしきい電圧より低く、他方は、そのしきい値よりも高い。

[0174]

第1トランジスタ504および第1容量素子507は、1ビットメモリとして 動作し、第2トランジスタ505および第4トランジスタ512の動作を制御す る。

[0175]

第2トランジスタ505は、第1容量素子507の電圧に応じて、オンオフ制 御される。第2トランジスタ505は、オン動作時には、アナログ信号走査線5 02における選択パルスによって、第3トランジスタ506の動作を制御する。

[0176]

第3トランジスタ506は、アナログ信号走査線502により、第2トランジ スタ505を介して選択され、アナログ信号線503の信号をサンプルし、第2 容量素子508にホールドし、液晶509に電圧を印加する。

[0177]

第4トランジスタは、第1トランジスタと相補的に動作し、動作時に、第2容 量素子508および液晶509に書き込まれた電荷を放出する。

[0178]

予めデジタル信号走査線500およびデジタル信号線501により1ビットデ ータを各画素の第1容量素子507に書き込んだ後、アナログ信号走査線502

およびアナログ信号線503により、液晶509に電圧を印加する。

[0179]

ブロック511内の各画素の液晶509は、1ビットデータに応じてアナログ 信号線503の信号ないし、共通配線の電圧が印加される。

[0180]

次に、信号書き込みのタイミングについて説明する。

1ビットデータのマッピングと液晶509に印加するアナログ信号の書き込みの タイミングは、以下のようないくつかのタイミングがある。

[0181]

1) 画面全体に1ビットデータをマッピングした後、ライン毎にブロックを選 択して同一の信号をブロック内の各画素に印加する。

[0182]

2)i(iは自然数)番目のブロック内の各画素に1ビットデータをマッピングした後、同じくi番目のブロック内の各画素に同一の信号を印加する。

[0183]

3)i番目からj番目までのブロックの各画素に1ビットデータをマッピングした後、同じくi番目からj(jはiより大きい自然数)番目までのブロックにおいて ライン毎にブロックを選択して同一の信号をブロック内の各画素に印加する。

[0184]

4)1ビットデータのマッピングとアナログ信号の書き込みは、別々のアナロ グ信号走査線の接続されたブロックにおいては、同時に実行する。

これによりデータ信号書き込み時間を長くでき、高精細化を容易にする効果がある。

[0185]

以上のように、1ビットのデジタルデータを各画素にマッピングした後に、ブ ロックにおいて"1"の状態にある画素全てに同一のにアナログ信号を印加する構 成とすると、任意のサイズのブロックを形成できる。

[0186]

この方式により、実施形態5のようにブロックの行方向の画素数を列方向の画

素数より多くでき、信号クロック周波数を低下させる効果とデータ信号書き込み 時間を増大する効果とが得られる。

[0187]

【実施形態7】

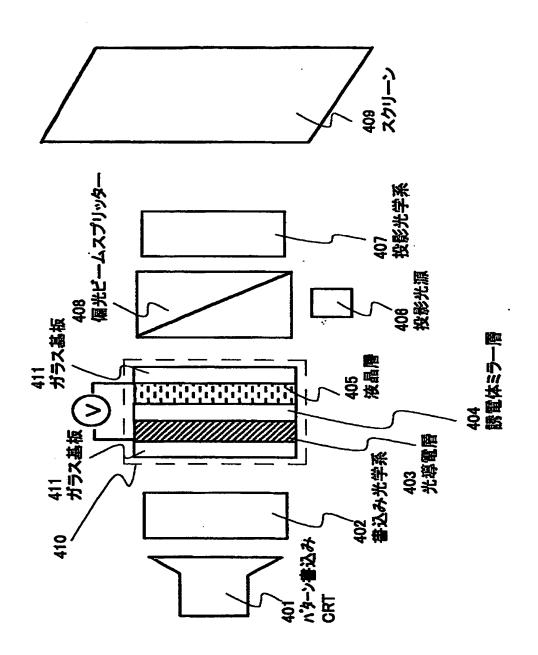

図14は、本発明による表示装置の実施形態7すなわち投射型ディスプレイの 構成を示す図である。本発明による実施形態7は、図6における表示モジュール 31として、図14に示される投射型ディスプレイとした以外は、実施形態1と 同じである。したがって、投射型ディスプレイについて説明する。

[0188]

図14に示すように、投射型ディスプレイは、パターン書き込みCRT401 と、書き込み光学系402と、パターン表示素子410と、投影光源406と、 投影光学系407と、偏光ビームスプリッタ408と、スクリーン409とから なる。

[0189]

パターン表示素子410は、透明電極(図示せず)が形成された2枚のガラス基 板411と、透明電極上に形成された光導電層403と、光導電層403上に形 成された誘電体ミラー層404と、2枚のガラス基板411に挟まれた液晶層4 05とからなる。

[0190]

パターン書き込みCRT401上には、1フレームから分けられたサブフレー ム毎に、図4(e)ないし(h)に示すような特定パターンが順次表示される。

[0191]

この特定パターンは、書き込み光学系402を経て光導電層403に転写され る。光導電層403では、転写された特定パターンの光強度にしたがって電気伝 導率の平面分布が生じる。その電気伝導率の値に応じて液晶層405に印加され る電圧が制御される。

[0192]

一方、投影光源406の光は、偏光ビームスプリッタ408を経て液晶層40 5を透過し、誘電体ミラー層404で反射され、再び液晶層405を透過するた

め、この光は、液晶層405によって制御される。

[0193]

その結果、誘電体ミラー層404で反射された反射光は、特定パターンの光強 度に応じて制御される。

【0194】

続いて、この反射光は、ビームスプリッタ408を通過し、投影光学系407 によってスクリーン409に投影される。

[0195]

この系において、液晶層405に印加される電圧は、複数の特定パターンが順 次に転写されることによって生じた実効値である。そのため、スクリーン409 上に結ばれる像は、これまでの実施形態と同様に所望の映像となる。

[0196]

本実施形態7によれば、パターン書き込みCRT401が表示する画像は、特 定パターンに限られており、簡便なCRTを利用できる。

[0197]

また、パターン書き込みを液晶モジュールで実行するのではなく、高速駆動C RTで実行するため、画質を向上するために加え合わせる特定パターン数を増大 することが可能である。

[0198]

なお、投射パターン表示源としては、パターン書き込みCRT401に限らず 、シリコン基板またはガラス基板上に形成された通常のアクティブマトリクス液 晶表示装置を用いたとしても、本発明による表示原理を適用できることは、いう までもない。

[0199]

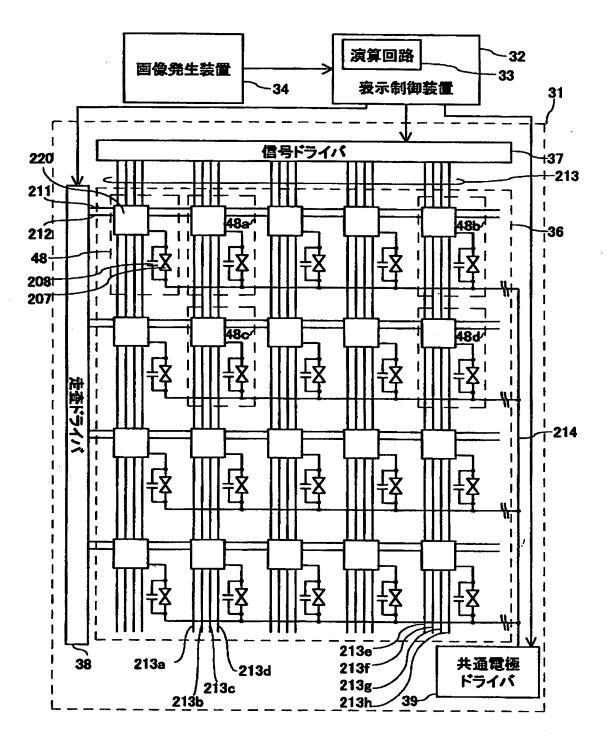

【実施形態8】

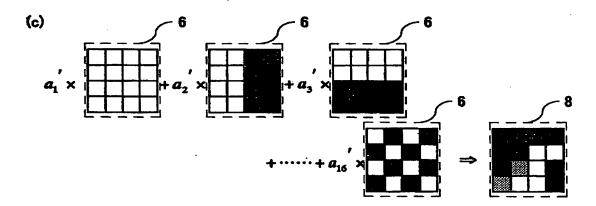

図15は、本発明による表示装置の実施形態8の構成を示す図である。本実施 形態8の表示装置は、表示パネル36として液晶パネルを用いた液晶表示装置で ある。

40

[0200]

特2000-173567

本実施形態8の液晶表示装置は、図15に示すように、画素48がマトリクス 状に配列した液晶パネル36と信号ドライバ37と走査ドライバ38と共通電極 ドライバ39とを備え、複数画素を1ブロック単位とし、ブロック単位中の複数 画素を同時に選択し、空間周波数の異なる特定パターンを1ないし複数個加え合 わせて画像を表示する表示モジュール31と、表示モジュール31を制御する表 示制御装置32と、ブロック毎に画像信号から空間周波数の異なる特定パターン を重み付けして発生させる演算回路33と、画像信号を発生する画像発生装置3 4とを備えている。

[0201]

信号ドライバ37には、信号線213が接続され、走査ドライバ38には、第 1走査線211および第2走査線212が接続され、共通電極ドライバ39には 、共通電極線214が接続されている。

[0202]

画素48には、加減算器220と容量素子208と液晶207に電圧を印加す るための信号電極(図示せず)および共通電極(図示せず)とが備えられており、信 号電極は、加減算器220を介して信号線213に接続され、共通電極は、共通 電極線214に接続されている。

[0203]

また、列方向に順に、R画素とG画素とB画素とが並んでいる。

[0204]

本実施形態8の画素部分の断面図は、図7に示すように、実施形態1に同じで あるため説明を省略する。

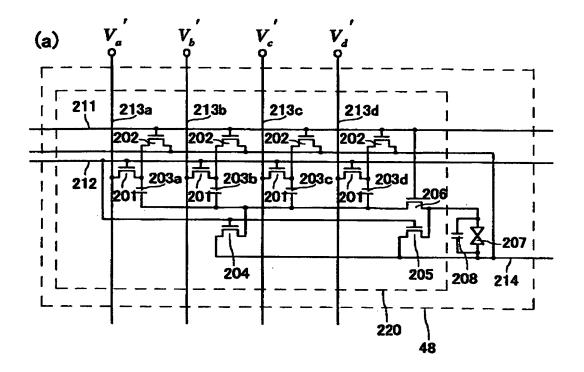

[0205]

図16は、図15の加減算器220の構成および動作を説明する図である。加 減算器220には、第1TFT201と第2TFT202と第3TFT204と 第4TFT205と第5TFT206と容量素子203a, 203b, 203c , 203dとが備えられている。容量素子203a, 203b, 203c, 20 3dの電荷容量は、全て等しく、C<sub>sig</sub>である。

[0206]

容量素子203a,203b,203c,203dは、第1TFT201を介 して、それぞれ信号線213a,213b,213c,213dに接続され、ま た第2TFT202および第3TFT204を介して共通線214に接続され、 また第5TFT206を介して液晶207および容量素子208に接続される。

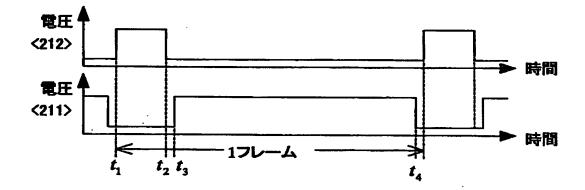

[0207]

図16(b)におけるt<sub>1</sub>のとき、第2走査線212にアドレス信号が与えられ 、第1TFT201および第3TFT204および第4TFT205が選択され ると、信号線213a, 213b, 213c, 213dに与えられた電圧が、そ れぞれ容量素子203a, 203b, 203c, 203dに保持される。

[0208]

同時に、容量素子208および液晶207に蓄えられていた電荷がリセットされる。

[0209]

ここで、信号線213a,213b,213c,213dに与える電圧を、それぞれ $V_a'$ , $V_b'$ , $V_c'$ , $V_d'$ とすると、容量素子203a,203b,203c,203dに蓄えられる電荷は、全体で $C_{sig}(V_a' + V_b' + V_c' + V_d')$ となる。

[0210]

続いて、図16(b)におけるt<sub>2</sub>のとき第1TFT201および第3TFT2 04および第4TFT205がオフし、t<sub>3</sub>のとき第1走査線211にアドレス 信号が与えられ、第2TFT202および第5TFT206が選択されると、容 量素子203a, 203b, 203c, 203dに蓄えられていた電荷C<sub>sig</sub> ( $V_a' + V_b' + V_c' + V_d'$ )が、容量素子203a, 203b, 203c , 203d, 208および液晶207に再分配される。

[0211]

ここで、液晶207の電荷容量を $C_{1c}$ 、容量素子208の電荷容量を $C_{st}$ gとすると、液晶207に印加される電圧 $V_{1c}$ は、数式10のようになる。

[0212]

【数10】

$$V_{lc} = \frac{C_{sig}}{4C_{sig} + C_{stg} + C_{lc}} \left( V_{a}' + V_{b}' + V_{c}' + V_{d}' \right)$$

以上のように、液晶207には、信号線213a, 213b, 213c, 21 3dに与えられた電圧の和に比例した電圧が印加される。

[0213]

次に、図15の演算回路33において、空間周波数の異なる特定パターンに重 み付けを実行する方法について説明する。

[0.214]

本実施形態8では、画素内の加減算器を利用して、空間周波数の異なる特定パ ターンを加え合わせるため、演算回路33では、数式5による「擬似直交変換法 」ではなく、一般的な直交変換であるアダマール変換を利用する。

[0215]

ここでは、図15の画素48a,48b,48c,48dからなる、行方向に 2個、列方向に2個の2×2のブロックを例にとって説明する。

[0216]

はじめに、画像発生装置から送られてきた画素48a,48b,48c,48 dの階調信号 $x_a$ , $x_b$ , $x_c$ , $x_d$ より、液晶の透過率一電圧特性に基づいて、液晶に印加すべき「目標電圧」 $V_a$ , $V_b$ , $V_c$ , $V_d$ を図5に示すように決定する。

[0217]

このとき、「擬似直交変換法」では、数式9を満たす必要があったが、本実施 形態8では、その必要がない。そのため、液晶の透過率-電圧特性には、図5に 示すような急峻な特性は、要求されない。

[0218]

次に、「目標電圧」 $V_a$ ,  $V_b$ ,  $V_c$ ,  $V_d$ に数式11に示すアダマール変換 を施して、特定パターンの重み $a_j$ (j=1,2,3,4)を求める。

【数11】

$$\begin{cases} a_{1} = C_{0} (V_{a} + V_{b} + V_{c} + V_{d}) \\ a_{2} = C_{0} (V_{a} - V_{b} + V_{c} - V_{d}) \\ a_{3} = C_{0} (V_{a} + V_{b} - V_{c} - V_{d}) \\ a_{4} = C_{0} (V_{a} - V_{b} - V_{c} + V_{d}) \end{cases}$$

【数12】

$$C_0 = \frac{4C_{sig} + C_{stg} + C_{lc}}{4C_{sig}}$$

ここで、係数C<sub>0</sub>は、通常のアダマール変換と異なるが、これは、数式10に 示すように、逆変換が通常のアダマール変換と異なるためである。

[0221]

図17は、得られた重み $a_j$ と特定パターンとの関係を示す図である。 重み $a_1$ に対応する特定パターンは、図17(a)に示すように、画素14a, 1 4b, 14c, 14dにそれぞれ信号 $a_1$ ,  $a_1$ ,  $a_1$ ,  $a_1$  を与えることで形 成する。

[0222]

重みa<sub>2</sub>に対応する特定パターンは、図17(b)に示すように、画素14a, 14b, 14c, 14dにそれぞれ信号a<sub>2</sub>, -a<sub>2</sub>, a<sub>2</sub>, -a<sub>2</sub>を与えるこ とで形成する。

[0223]

重みa3に対応する特定パターンは、図17(c)に示すように、画素14a,

44

出証特2000-3095497

14b, 14c, 14dにそれぞれ信号 a<sub>3</sub>, a<sub>3</sub>, - a<sub>3</sub>, - a<sub>3</sub>を与えるこ とで形成する。

[0224]

重み $a_4$ に対応する特定パターンは、図17(d)に示すように、画素14a, 14b, 14c, 14dにそれぞれ信号 $a_4$ ,  $-a_4$ ,  $-a_4$ ,  $a_4$ を与えるこ とで形成する。

[0225]

ここで、正の信号が与えられた画素を白色、負の信号が与えられた画素を灰色 として識別すると、図17(a)ないし(d)が示すように、空間周波数の異なる特 定パターンが形成されていることが分かる。

[0226]

このような特定パターンを、以下に説明するように画素内で加え合わせること によって、原画像を再現できる。

[0227]

図15の画素48a,48b,48c,48dに注目する。画素48a,48 bが接続された第2走査線212が選択されるときに、信号線213a,213 eにそれぞれ電圧 $a_1$ , $a_1$ を与え、信号線213b,213fにそれぞれ電圧 $a_2$ , $-a_2$ を与え、信号線213c,213gにそれぞれ電圧 $a_3$ , $a_3$ を与え、信号線213d,213hにそれぞれ電圧 $a_4$ , $-a_4$ を与える。

[0228]

続いて、第2走査線212がオフされ、第1走査線211が選択されると、画素48a,48bの液晶207には、数式10に従った電圧が印加される。すなわち、画素48a,48bの液晶に印加される電圧 $V_{1ca}$ , $V_{1cb}$ は、数式13のようになり、「目標電圧」が印加される。

[0229]

【数13】

$$\begin{cases} V_{lc_a} = \frac{1}{4C_0} (a_1 + a_2 + a_3 + a_4) = \frac{1}{4C_0} 4C_0 V_a = V_a \\ V_{lc_b} = \frac{1}{4C_0} (a_1 - a_2 + a_3 - a_4) = \frac{1}{4C_0} 4C_0 V_b = V_b \end{cases}$$

このことは、図17に示した特定パターンのうち、画素14a,14bからな る特定パターンの加え合わせが終了したことに相当する。

[0230]

次に、画素48c,48dが接続された第2走査線212が選択されるときに、信号線213a,213eにそれぞれ電圧 $a_1$ , $a_1$ を与え、信号線213b,213fにそれぞれ電圧 $a_2$ , $-a_2$ を与え、信号線213c,213gにそれぞれ電圧 $-a_3$ , $-a_3$ を与え、信号線213d,213hにそれぞれ電圧 $-a_4$ , $a_4$ を与える。

[0231]

続いて、第2走査線212がオフされ、第1走査線211が選択されると、画素48c,48dの液晶207には、数式10に従った電圧が印加される。すなわち、画素48c,48dの液晶に印加される電圧V1cc,V1cdは、数式14のようになり、「目標電圧」が印加される。

[0232]

【数14】

$$\begin{cases} V_{lc_{c}} = \frac{1}{4C_{0}} (a_{1} + a_{2} - a_{3} - a_{4}) = \frac{1}{4C_{0}} 4C_{0}V_{c} = V_{c} \\ V_{lc_{d}} = \frac{1}{4C_{0}} (a_{1} - a_{2} - a_{3} + a_{4}) = \frac{1}{4C_{0}} 4C_{0}V_{d} = V_{d} \end{cases}$$

このことは、図17に示した特定パターンのうち、画素14c,14dからな

る特定パターンの加え合わせが終了したことに相当する。

[0233]

このように、2行の走査が終了した時点で、2×2のブロックにおける特定パ ターンの加え合わせが終了する。

[0234]

同様にして、全ての行が走査されると、全てのブロックにおいて走査が終了し 、画像が再現される。

[0235]

このように、本実施形態8では、「擬似直交変換表示法」と異なり、1つのフ レームをサブフレームに分けることなく、全ての行の走査を一度事項すると、加 え合わせが終了する。

[0236]

本実施形態8によれば、次のような効果が得られる。全ての行の走査を一度実 行して画像を表示するため、信号データ書き込み時間がブロックのサイズなどに 影響を受けることなく一定である。

[0237]

また、数式11によって重み付けされた特定パターンのうち、その一部のみを 加え合わせて表示できるため、「擬似直交変換表示法」と同様の原理で、信号ク ロック周波数を低下できる。

[0238]

さらに、一般的なアダマール変換を使用しているため、演算回路33の負担が 少なく、かつ高速演算が可能である。

[0239]

なお、図16(a)における、第1TFT201および第2TFT202および 容量素子203a, 203b, 203c, 203dは、加え合わせる特定パター ン数Np個だけ用意すればいいことは、いうまでもない。

[0240]

【実施形態9】

図18は、本発明による表示装置の実施形態9の構成を示す図である。本発明

出証特2000-3095497

による実施形態9は、図18に示すように、図8における演算回路33が表示制 御装置32に含まれるのではなく、画像発生装置34に含まれること以外は、実 施形態2に同じである。

[0241]

本実施形態9によれば、表示制御装置32から表示モジュール31に送られる 信号量の削減のみならず、画像発生装置34から表示制御装置32への信号量も 軽減でき、表示装置の高精細化が容易になる。

[0242]

【実施形態10】

図19は、本発明による表示装置の実施形態10の構成を示す図である。本発 明による実施形態10は、図19に示すように、図11における演算回路33が 表示制御装置32に含まれるのではなく、表示モジュール31に含まれること以 外は、実施形態5に同じである。

[0243]

本実施形態10によれば、画像発生装置34および表示制御装置32は、既存 のものを利用できる上に、実施形態5と同様に、データ信号書き込み時間の増大 の効果が得られる。

[0244]

【発明の効果】

本発明によれば、表示装置において、空間周波数の異なる特定パターンを1ないし複数個加え合わせて画像を表示する表示モジュールを備えることにより、信 号クロック周波数を低下させるとともに、信号書き込み時間を増大でき、開口率 を上げて、超高精細表示かつ高速動画表示が可能な表示装置が得られる。

【図面の簡単な説明】

【図1】

本発明による表示装置の全体構成を示すブロック図および動作原理を示す図である。

【図2】

従来の表示装置の一般的構成を示す図である。

【図3】

従来の表示装置の系統構成および表示パネル内の構成を示す図である。

【図4】

本発明により画素上で特定パターンを表示する原理を説明する図である。

【図5】

液晶に印加すべき電圧 $V_a$ ,  $V_b$ ,  $V_c$ ,  $V_d$ の決定の様子を示す図である。

【図6】

本発明による表示装置の実施形態1の構成を示す図である。

【図7】

本実施形態1の液晶パネルの構成を説明する画素部分の断面構造を示す図である。

【図8】

本発明による表示装置の実施形態2の構成を示す図である。

【図9】

本発明による表示装置の実施形態3の構成を示す図である。

【図10】

本発明による表示装置の実施形態4の構成を示す図である。

【図11】

本発明による表示装置の実施形態5の構成を示す図である。

【図12】

4×1のブロックにおいて特定パターンを表示する原理を説明する図である。

【図13】

本発明による表示装置の実施形態6の構成を示す図である。

【図14】

本発明による表示装置の実施形態7すなわち投射型ディスプレイの構成を示す 図である。

【図15】

本発明による表示装置の実施形態8の構成を示す図である。

【図16】

【図17】

本発明で得られた重みa;と特定パターンとの関係を示す図である。

【図18】

本発明による表示装置の実施形態9の構成を示す図である。

【図19】

本発明による表示装置の実施形態10の構成を示す図である。

【符号の説明】

1,21,31 表示モジュール

2,22,32 表示制御装置

3,33 演算回路

4,24,34 画像発生装置

6 特定パターン

7,8 画像

11a,11b,42,42R1,42G1,42B1,42R2,42G2,42B2 ,42R3,42G3,213,213a,213b,213c,213d,213e, 213f,213g,213h 信号線

12a,12b,12c,12d,44a,44b,44c,44d,44aR,44a G,44aB,44bR,44bG,44bB,44cR,44cG,44cB,44d R,44dG,44dB, 44' 対向信号線

13 画素電極

13a,68 信号電極

13b,69 対向信号電極

14a,14b,14c,14d,25,48,48a,48b,48c,48d,48e ,48f,48g,48h,510 画素

26,36 表示パネル

35 対向信号ドライバ

37 信号ドライバ

38 走査ドライバ

特2000-173567

- 39 共通電極ドライバ 41,41a,41b,41c,41d 走査線 43,214 共通電極線 4 4 R 1, 4 4 G 1, 4 4 B 1, 4 4 R 2, 4 4 G 2, 4 4 B 2, 4 4 R 3, 4 4 G 3, 44R1a,44R1b,44R1c,44R1d,44G1a,44G1b,44G 1 c, 4 4 G 1 d, 4 4 R 2 a, 4 4 R 2 b, 4 4 R 2 c, 4 4 R 2 d 対向信号共 通線 45,203a,203b,203c,203d,208 容量素子 46,70,207,509 液晶 47 薄膜トランジスタ(TFT) 61 偏光板 62,67 基板 63,64 絶縁膜 65 配向膜 66 カラーフィルタ 81 圧縮率調整装置 82 高圧縮演算回路 201 第1TFT 202 第2777 204 第3TFT 205 第4TFT 206 第5TFT 211 第1走査線 212 第2走査線 220 加減算器 401 パターン書き込みCRT 402 書き込み光学系 403 光導電層

- 404 誘電体ミラー層

405 液晶層

-

- 406 投影光源

- 407 投影光学系

- 408 偏光ビームスプリッタ

- 409 スクリーン

- 410 パターン表示素子

- 411 ガラス基板

- 500 デジタル信号走査線

- 501 デジタル信号線

- 502 アナログ信号走査線

- 503 アナログ信号線

- 504 第1トランジスタ

- 505 第2トランジスタ

- 506 第3トランジスタ

- 507 第1容量素子

- 508 第2容量素子

- 511 ブロック

- 512 第4トランジスタ

【図1】

【図2】

出証特2000-3095497

【図3】

【図4】

(f)

46 4d 14c

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

10

**\_**

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

(a)

•

ę

.

【図18】

## 【図19】

【書類名】 要約書

【要約】

【課題】 クロック周波数を低下させ、信号書き込み時間を増大させ、開口率を 上げ、高精細表示かつ高速動画表示が可能な表示装置を提供する。

【解決手段】 複数画素を1ブロック単位とし、ブロック単位中の複数画素を同時に選択し、空間周波数の異なる特定パターン6を1ないし複数個加え合わせて 画像を表示する表示モジュール1と、表示モジュール1を制御する表示制御装置 2と、ブロック毎に画像信号から空間周波数の異なる特定パターン6を重み付け して発生させる演算回路3と、画像信号を発生する画像発生装置4とを備える表 示装置を構成する。

クロック周波数を低下させ、信号書き込み時間を増大させ、開口率を上げて、 超高精細表示かつ高速動画表示が可能な表示装置が得られる。

1

【選択図】 図1

特2000-173567

## 出願人履歴情報

識別番号

۶

7 ·

[000005108]

2. 変更年月日 1990年 8月31日

[変更理由] 新規登録

住所 東京都千代田区神田駿河台4丁目6番地

氏名 株式会社日立製作所

Ţ